# SYSMAC CQM1/CPM1/CPM1A/SRM1 Programmable Controllers

## CQM1/CPM1/CPM1A/SRM1 Programmable Controllers

### **Programming Manual**

Revised May 1999

### Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

- **DANGER** Indicates an imminently hazardous situation which, if not avoided, will result in death or serious injury.

- **WARNING** Indicates a potentially hazardous situation which, if not avoided, could result in death or serious injury.

- **Caution** Indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury, or property damage.

### **OMRON Product References**

All OMRON products are capitalized in this manual. The word "Unit" is also capitalized when it refers to an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation "Ch," which appears in some displays and on some OMRON products, often means "word" and is abbreviated "Wd" in documentation in this sense.

The abbreviation "PC" means Programmable Controller and is not used as an abbreviation for anything else.

### Visual Aids

The following headings appear in the left column of the manual to help you locate different types of information.

- **Note** Indicates information of particular interest for efficient and convenient operation of the product.

- 1, 2, 3... 1. Indicates lists of one sort or another, such as procedures, checklists, etc.

#### © OMRON, 1993

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

### About this Manual:

This manual describes programming of the CQM1, CPM1, CPM1A, and SRM1 Programmable Controllers, including memory structure, memory contents, ladder-diagram instructions, etc., and includes the sections described below. Refer to the *CQM1 Operation Manual, CPM1 Operation Manual, CPM1A Operation Manual, and SRM1 Master Control Units Operation Manual for hardware information and Pro*gramming Console operating procedures. Refer to the *SSS Operation Manual: C-series PCs* for SSS operating procedures.

**Note** The SRM1 is a specialized programmable controller and is normally called a CompoBus/S Master Control Unit. The SRM1, however, is programmed in the same way as the other Programmable Controllers and it is treated and referred to as a PC in this manual.

Please read this manual carefully and be sure you understand the information provided before attempting to program and operate the CQM1, CPM1, CPM1A or SRM1.

**Section 1** explains the PC Setup and related PC functions, including interrupt processing and communications. The PC Setup can be used to control the operating parameters of the PC.

**Section 2** provides an introduction to new PC features, including the new instructions available through expansion instructions and a new monitoring feature call differential monitoring.

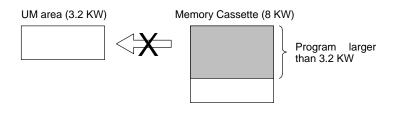

**Section 3** describes the structure of the PC's memory areas, and explains how to use them. It also describes Memory Cassette operations used to transfer data between the CQM1 and a Memory Cassette.

**Section 4** explains the basic steps and concepts involved in writing a basic ladder diagram program. It introduces the instructions that are used to build the basic structure of the ladder diagram and control its execution.

*Section 5* individually describes the ladder-diagram programming instructions that can be used with the PC.

**Section 6** explains the methods and procedures for using host link commands, which can be used for host link communications via the PC ports.

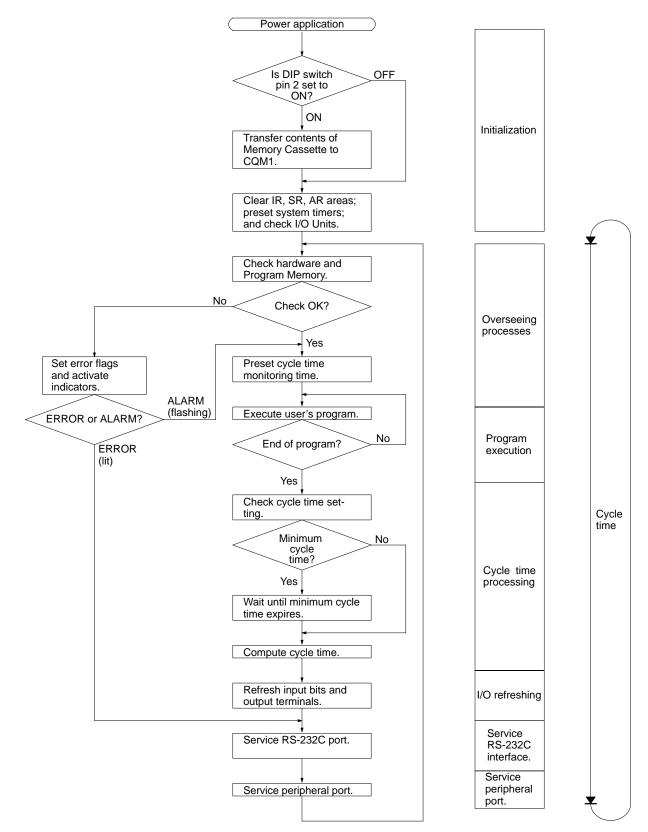

**Section 7** explains the internal processing of the PCs, and the time required for processing and execution. Refer to this section to gain an understanding of the precise timing of PC operation.

**Section 8** describes how to diagnose and correct the hardware and software errors that can occur during PC operation.

The following appendices are also provided: A Programming Instructions, B Error and Arithmetic Flag Operation, C Memory Areas, D Using the Clock Function, E I/O Assignment Sheet, F Program Coding Sheet, G List of FAL Numbers, H Extended ASCII, and I CPM1A and CPM1 Memory Area Comparison.

# **WARNING** Failure to read and understand the information provided in this manual may result in personal injury or death, damage to the product, or product failure. Please read each section in its entirety and be sure you understand the information provided in the section and related sections before attempting any of the procedures or operations given.

| PRE   | CAUTIONS                                         | xiii |

|-------|--------------------------------------------------|------|

|       | ended Audience                                   | xiv  |

| 2 Ge  | neral Precautions                                | xiv  |

| 3 Sat | fety Precautions                                 | xiv  |

| 4 Ap  | plication Precautions                            | xiv  |

| SEC   | TION 1                                           |      |

| PC S  | Setup and Other Features                         | 1    |

| 1-1   | PC Setup                                         | 3    |

| 1-2   | Basic PC Operation and I/O Processes             | 16   |

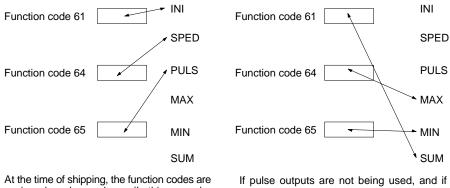

| 1-3   | Pulse Output Function (CQM1 Only)                | 22   |

| 1-4   | Pulse Output Function (CPM1A Only)               | 35   |

| 1-5   | CQM1 Interrupt Functions                         | 38   |

| 1-6   | CPM1/CPM1A Interrupt Functions                   | 67   |

| 1-7   | SRM1 Interrupt Functions                         | 83   |

| 1-8   | CompoBus/S Distributed I/O Functions (SRM1 Only) | 86   |

| 1-9   | Communications Functions                         | 87   |

| 1-10  | Calculating with Signed Binary Data              | 111  |

| SEC   | TION 2                                           |      |

| Spec  | ial Features                                     | 115  |

| 2-1   | Expansion Instructions (CQM1/SRM1 Only)          | 116  |

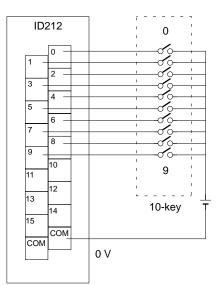

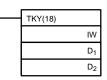

| 2-2   | Advanced I/O Instructions (CQM1 Only)            | 118  |

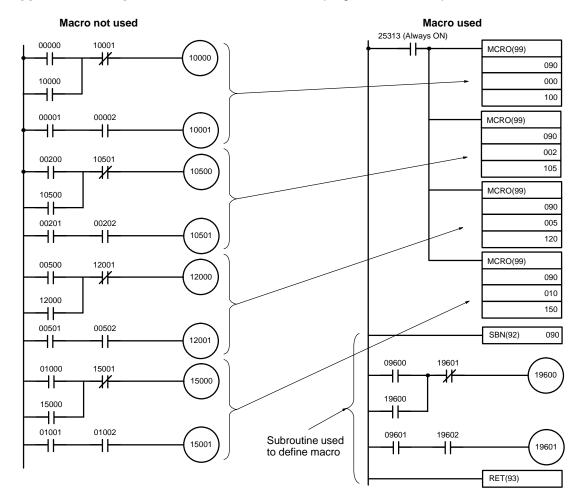

| 2-3   | Macro Function                                   | 128  |

| 2-4   | Differential Monitor                             | 129  |

| 2-5   | Analog Settings (CQM1-CPU42-EV1/CPM1/CPM1A Only) | 129  |

| 2-6   | Quick-response Inputs (CPM1/CPM1A Only)          | 131  |

| SEC   | TION 3                                           |      |

| Men   | nory Areas                                       | 133  |

| 3-1   | CQM1 Memory Area Functions                       | 134  |

| 3-2   | CPM1/CPM1A Memory Area Functions                 | 139  |

| 3-3   | SRM1 Memory Area Functions                       | 143  |

| 3-4   | SRM1 Flash Memory                                | 145  |

| 3-5   | Using Memory Cassettes (CQM1 Only)               | 146  |

| SEC   | TION 4                                           |      |

|       | der-diagram Programming                          | 151  |

| 4-1   | Basic Procedure                                  | 152  |

| 4-2   | Instruction Terminology                          | 152  |

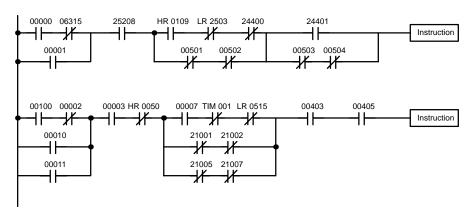

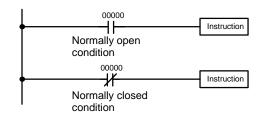

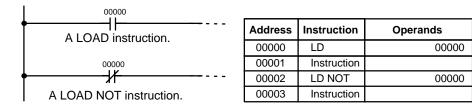

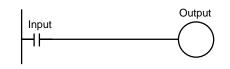

| 4-3   | Basic Ladder Diagrams                            | 153  |

| 4-4   | Controlling Bit Status                           | 173  |

| 4-5   | Work Bits (Internal Relays)                      | 175  |

| 4-6   | Programming Precautions                          | 177  |

| 4-7   | Program Execution                                | 179  |

| SEC  | TION 5                                                                                               |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | ruction Set                                                                                          | 181 |

| 5-1  | Notation                                                                                             | 184 |

| 5-2  | Instruction Format                                                                                   | 184 |

| 5-3  | Data Areas, Definer Values, and Flags                                                                | 184 |

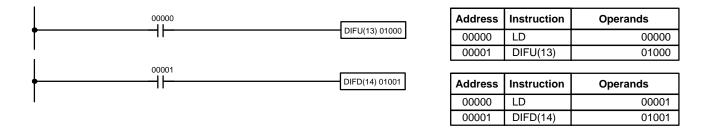

| 5-4  | Differentiated Instructions                                                                          | 186 |

| 5-5  | Coding Right-hand Instructions                                                                       | 186 |

| 5-6  | Instruction Tables                                                                                   | 190 |

| 5-7  | Ladder Diagram Instructions                                                                          | 196 |

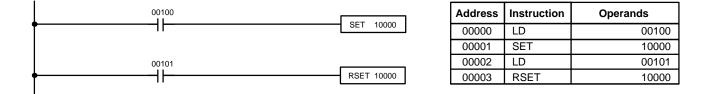

| 5-8  | Bit Control Instructions                                                                             | 197 |

| 5-9  | NO OPERATION – NOP(00)                                                                               | 201 |

| 5-10 | END – END(01)                                                                                        | 201 |

| 5-11 | INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03)                                                   | 201 |

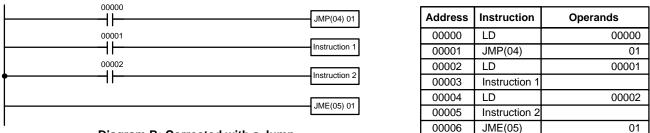

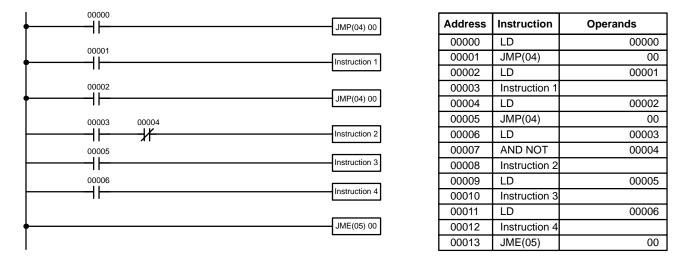

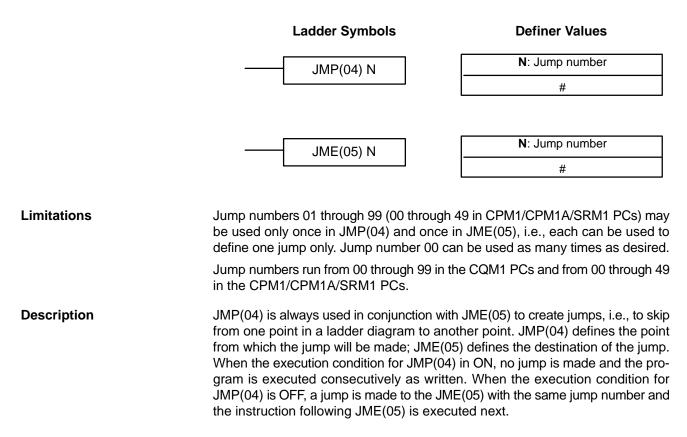

| 5-12 | JUMP and JUMP END – JMP(04) and JME(05)                                                              | 203 |

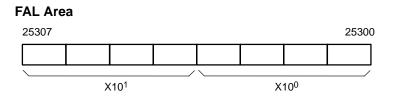

| 5-13 | User Error Instructions:<br>FAILURE ALARM AND RESET – FAL(06) and<br>SEVERE FAILURE ALARM – FALS(07) | 205 |

| 5-14 | Step Instructions:                                                                                   |     |

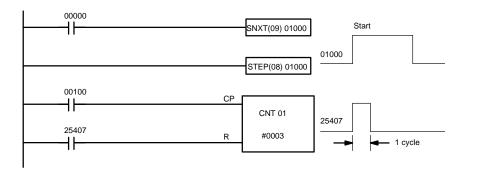

| _    | STÊP DEFINE and STEP START–STEP(08)/SNXT(09)                                                         | 206 |

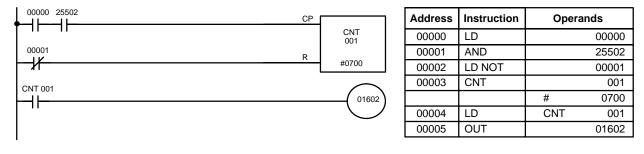

|      | Timer and Counter Instructions                                                                       | 208 |

|      | Shift Instructions                                                                                   | 224 |

|      | Data Movement Instructions                                                                           | 232 |

|      | Comparison Instructions                                                                              | 242 |

|      | Conversion Instructions                                                                              | 252 |

|      | BCD Calculation Instructions                                                                         | 278 |

| 5-21 | Binary Calculation Instructions                                                                      | 289 |

| 5-22 | · ·                                                                                                  | 300 |

|      | Logic Instructions                                                                                   | 308 |

|      | Increment/Decrement Instructions                                                                     | 311 |

|      | Subroutine Instructions                                                                              | 313 |

|      | Special Instructions                                                                                 | 315 |

|      | Communications Instructions                                                                          | 340 |

|      | Advanced I/O Instructions                                                                            | 345 |

|      | TION 6                                                                                               |     |

| Host | t Link Commands                                                                                      | 349 |

| 6-1  | Communications Procedure                                                                             | 350 |

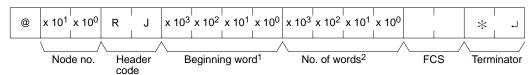

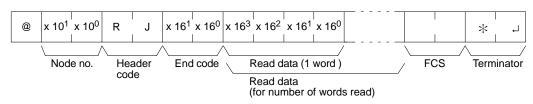

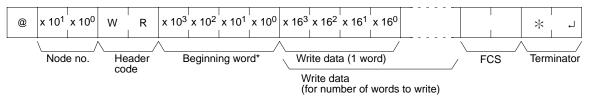

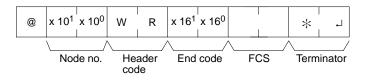

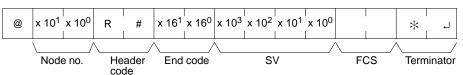

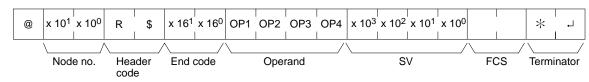

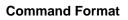

| 6-2  | Command and Response Formats                                                                         | 352 |

| 6-3  | Host Link Commands                                                                                   | 356 |

| SEC  | TION 7                                                                                               |     |

|      |                                                                                                      | 201 |

| PU   |                                                                                                      | 381 |

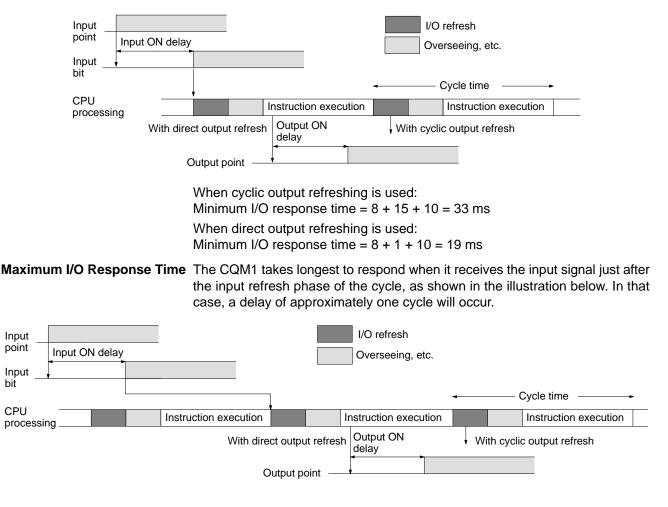

| 7-1  | CQM1 Cycle Time and I/O Response Time                                                                | 382 |

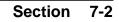

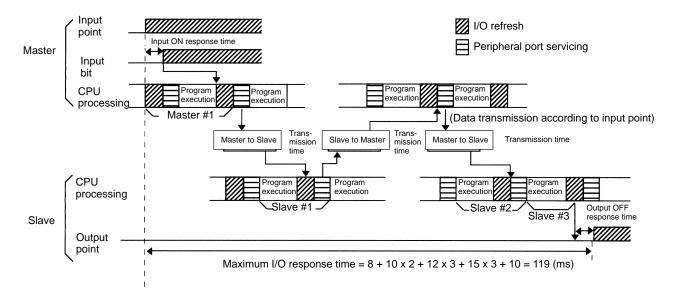

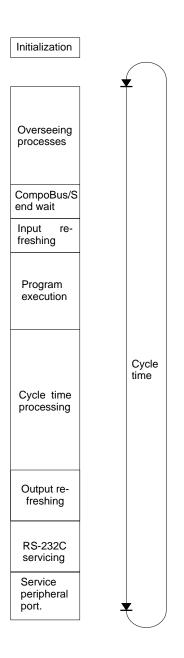

| 7-2  | CPM1/CPM1A Cycle Time and I/O Response Time                                                          | 400 |

| 7-3  | SRM1 Cycle Time and I/O Response Time                                                                | 411 |

| SEC  | TION 8                                                                                               |     |

|      |                                                                                                      | 100 |

| Irou | 8                                                                                                    | 423 |

| 8-1  | Introduction                                                                                         | 424 |

| 8-2  | Programming Console Operation Errors                                                                 | 424 |

| 8-3  | Programming Errors                                                                                   | 425 |

| 8-4  | User-defined Errors                                                                                  | 426 |

| 8-5  | Operating Errors                                                                                     | 427 |

| 8-6  | Error Log                                                                                            | 430 |

| 8-7  | Host Link Errors                                                                                     | 432 |

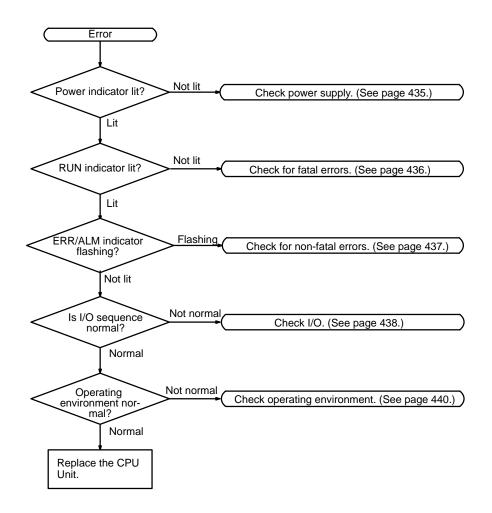

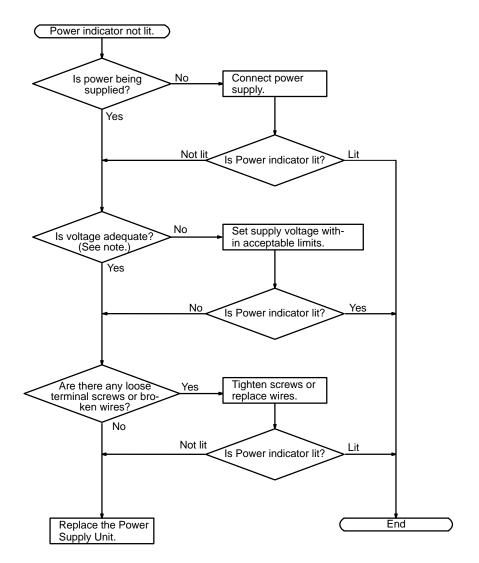

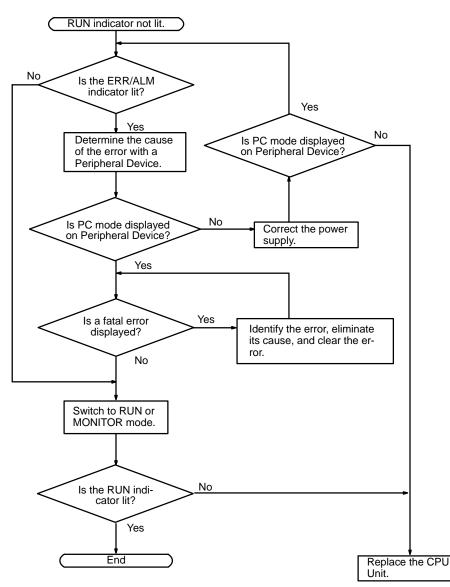

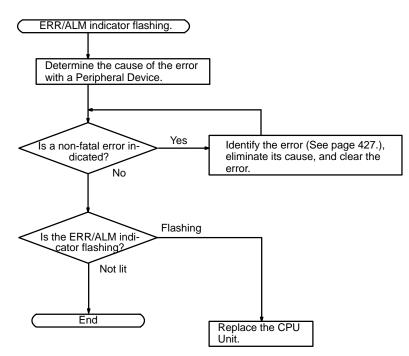

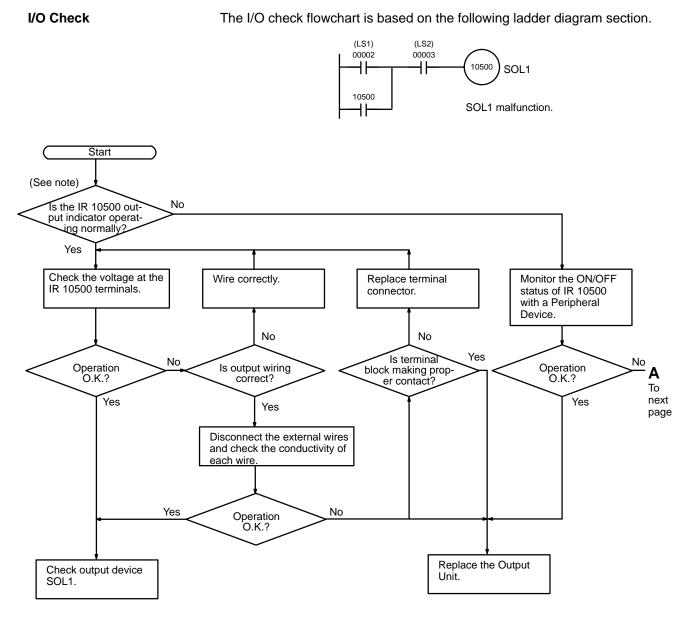

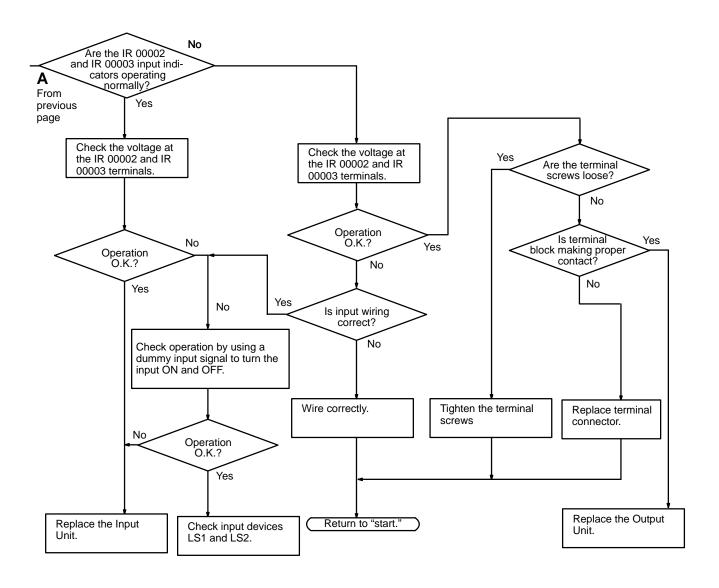

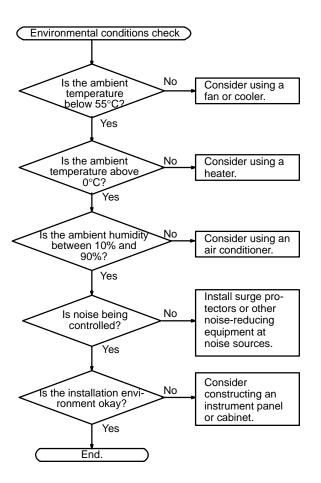

| 8-8  | Troubleshooting Flowcharts                                                                           | 434 |

### Appendices

| A Programming Instructions                   | 441        |

|----------------------------------------------|------------|

| B Error and Arithmetic Flag Operation        | 447        |

| C Memory Areas                               | 451        |

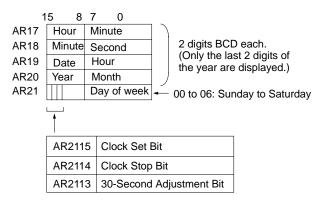

| D Using the Clock Function                   | 469        |

| E I/O Assignment Sheet                       | 471        |

| F Program Coding Sheet                       | 473        |

| G List of FAL Numbers                        | 477        |

| H Extended ASCII                             | 479        |

| I CPM1/CPM1A and CQM1 Memory Area Comparison | 481        |

| Glossary                                     | 483        |

| Index                                        | <b>499</b> |

| Revision History                             | 507        |

### PRECAUTIONS

This section provides general precautions for using the Programmable Controller (PC) and related devices.

The information contained in this section is important for the safe and reliable application of the Programmable Controller. You must read this section and understand the information contained before attempting to set up or operate a PC system.

| 1 Intended Audience       | xiv |

|---------------------------|-----|

| 2 General Precautions     | xiv |

| 3 Safety Precautions      | xiv |

| 4 Application Precautions | xiv |

### 1 Intended Audience

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

- Personnel in charge of installing FA systems.

- Personnel in charge of designing FA systems.

- Personnel in charge of managing FA systems and facilities.

#### 2 General Precautions

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that may have a serious influence on lives and property if used improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are sufficient for the systems, machines, and equipment, and be sure to provide the systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the Unit. Be sure to read this manual before attempting to use the Unit and keep this manual close at hand for reference during operation.

**WARNING** It is extremely important that a PC and all PC Units be used for the specified purpose and under the specified conditions, especially in applications that can directly or indirectly affect human life. You must consult with your OMRON representative before applying a PC System to the above-mentioned applications.

#### 3 Safety Precautions

**Caution** Execute online edit only after confirming that no adverse effects will be caused by extending the cycle time. Otherwise, the input signals may not be readable.

**Caution** Confirm safety at the destination node before transferring a program to another node or changing the I/O memory area. Doing either of these without confirming safety may result in injury.

### 4 Application Precautions

Observe the following precautions when using the PC System.

**Caution** Failure to abide by the following precautions could lead to faulty operation of the PC or the system, or could damage the PC or PC Units. Always heed these precautions.

- Fail-safe measures must be taken by the customer to ensure safety in the event of incorrect, missing, or abnormal signals caused by broken signal lines, momentary power interruptions, or other causes.

- Interlock circuits, limit circuits, and similar safety measures in external circuits (i.e., not in the Programmable Controller) must be provided by the customer.

- Check the user program for proper execution before actually running it on the Unit. Not checking the program may result in an unexpected operation.

- Confirm that no adverse effect will occur in the system before attempting any of the following. Not doing so may result in an unexpected operation.

- Changing the operating mode of the PC.

- Force-setting/force-resetting any bit in memory.

- Changing the present value of any word or any set value in memory.

- Resume operation only after transferring to the new CPU Unit the contents of the DM and HR Areas required for resuming operation. Not doing so may result in an unexpected operation.

- Do not place objects on top of the cables. Doing so may break the cables.

- Before touching the Unit, be sure to first touch a grounded metallic object in order to discharge any static built-up. Not doing so may result in malfunction or damage.

- Do not touch the Expansion I/O Unit Connecting Cable while the power is being supplied in order to prevent any malfunction due to static electricity.

- **Caution** Always clear memory before beginning to program the CPM1, CPM1A or SRM1. Although memory is cleared before the CPU Unit is shipped (except for bits with specific functions), AR 1314, which turns ON when the internal capacitor cannot back up memory, may have turned ON during shipment.

- **Caution** If the CPM1 or CPM1A will be turned OFF for periods exceeding the data backup period of the internal capacitor, design the system so that it will not be influenced if data in the DM, HR, and CNT areas is cleared when power is turned OFF.

- **Caution** Either switch the CPM1 or CPM1A to RUN or MONITOR mode, or turn OFF and ON power to the CPM1 or CPM1A after changing from a Programming Device any data that is backed up in flash memory. This data includes the user program, read-only DM area (DM 6144 to DM 6599), and the PC Setup (DM 6600 to DM 6655).

- The user program and memory area data in the CPM1 or CPM1A are backed up either by an internal capacitor or in flash memory as shown in the following table.

| Backup method      | Data                                                          |

|--------------------|---------------------------------------------------------------|

| Internal capacitor | Read/write DM area (DM 0000 to DM 0999, DM 1022, and DM 1023) |

|                    | Error log area (DM 1000 to DM 1021)                           |

|                    | HR area (HR 00 to HR 19)                                      |

|                    | Counter area (CNT 000 to CNT 127)                             |

| Flash memory       | User program                                                  |

|                    | Read-only DM area (DM 6144 to DM 6599)                        |

|                    | PC Setup (DM 6600 to DM 6655)                                 |

- Note 1. The IR, TR, LR, and timer areas are not normally backed up when power is turned OFF and all contents will be cleared the next time power is turned ON. (The PC Setup setting in DM 6601 can be used to back up this data. Refer to details on the PC Setup later in this manual for details.)

- 2. The bits in the AR and SR areas have special functions and are set according to these functions when power is turned ON.

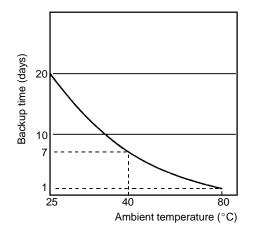

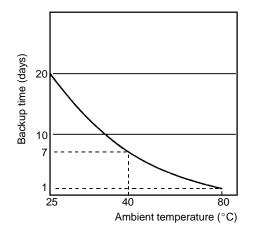

The capacitor backup time depends on the ambient temperature, as shown in the following graph. The backup time, however, assumes that the capacitor is fully charged, which requires that power be supplied to the CPU Unit continuously for at least 15 minutes.

If the power remains OFF for a period exceeding the data backup period, AR 1314 will turn ON to indicate that the capacitor can no longer back up data and the data backed up by the capacitor will be cleared. AR 1314 will remain ON unless it is turned OFF using I/O monitor operations, using memory clear operations, or from the user program.

If desired, the PC Setup setting in DM 6604 can be set to create a fatal error and thus stop the system when AR 1314 goes ON.

- The data stored in flash memory will not be lost even if power remains OFF for a period exceeding the data backup period, because the data stored in flash memory will be read to the CPU Unit when the CPM1 or CPM1A is turned ON.

- If the power is turned OFF without changing the mode from PROGRAM mode to RUN or MONITOR mode after having made changes in the data that is backed up in flash memory, the changes will not be written to flash memory. If the power is then left OFF for more than 20 days (at 25°C), the changes (i.e., the contents of the RAM) will be erased and the data values will become undefined.

- (!) Caution Be sure that the SRM1 system is not influenced by any undefined data if the data in the DM, HR, or CNT area is cleared when the SRM1 has been turned OFF for a period exceeding the data backup period of the internal lithium battery. If the AR 1414 flag is ON, the data will be held unless it is turned OFF using the I/O Monitor operation, instructions, etc. The system can be stopped by designating DM 6604 in the PC Setup so that a memory error occurs when the power interruption hold area is not held (with AR 1314 ON)

- A lithium battery in the CPU Unit is used to back up the counter values and the contents of the DM area, and HR area. The deterioration of the lithium battery capacity depends on the ambient temperature. The standard service life is 12 years at an ambient temperature of 40°C when operating 8 hours a day.

If the power remains off for a period exceeding the data backup period, the contents of the Data Memory (DM), Hold Relay (HR), and Counter (CNT) Areas in the CPU Unit may be cleared and the AR 1314 flag (which turns ON when the power interruption hold area is not held) may turn ON.

If the contents of the CPU Unit's program area are lost, the program stored in flash memory will be read to the CPU Unit's program area when the SRM1 is started up because the contents in the read-only area (DM 6144 through DM 6599) and PC Setup (DM 6600 through DM 6655) will be written to flash memory.

However, if the power is turned OFF without changing the mode even if changes are made in the read-only DM area (DM 6144 through DM 6599), or PC Setup (DM 6600 through DM 6655) using a peripheral device, the contents of changes will not be written to flash memory. Although the data in these areas is backed up by the lithium battery, contents of changes will disappear if the service life of the lithium battery expires. In this case, programs in the flash memory will be automatically read into the user program memory.

The changes can be saved by switching the SRM1 to RUN or MONITOR mode or turning OFF and restarting the SRM1 soon after the changes are made.

| PRE   | <b>CAUTIONS</b>                                  | xiii |  |

|-------|--------------------------------------------------|------|--|

| 1 Int | ended Audience                                   | xiv  |  |

| 2 Ge  | 2 General Precautions                            |      |  |

| 3 Sa  | 3 Safety Precautions                             |      |  |

| 4 Ap  | 4 Application Precautions                        |      |  |

| SEC   | CTION 1                                          |      |  |

| PC S  | Setup and Other Features                         | 1    |  |

| 1-1   | PC Setup                                         | 3    |  |

| 1-2   | Basic PC Operation and I/O Processes             | 16   |  |

| 1-3   | Pulse Output Function (CQM1 Only)                | 22   |  |

| 1-4   | Pulse Output Function (CPM1A Only)               | 35   |  |

| 1-5   | CQM1 Interrupt Functions                         | 38   |  |

| 1-6   | CPM1/CPM1A Interrupt Functions                   | 67   |  |

| 1-7   | SRM1 Interrupt Functions                         | 83   |  |

| 1-8   | CompoBus/S Distributed I/O Functions (SRM1 Only) | 86   |  |

| 1-9   | Communications Functions                         | 87   |  |

|       | Calculating with Signed Binary Data              | 111  |  |

| SEC   | CTION 2                                          |      |  |

| Spec  | cial Features                                    | 115  |  |

| 2-1   | Expansion Instructions (CQM1/SRM1 Only)          | 116  |  |

| 2-2   | Advanced I/O Instructions (CQM1 Only)            | 118  |  |

| 2-3   | Macro Function                                   | 128  |  |

| 2-4   | Differential Monitor                             | 129  |  |

| 2-5   | Analog Settings (CQM1-CPU42-EV1/CPM1/CPM1A Only) | 129  |  |

| 2-6   | Quick-response Inputs (CPM1/CPM1A Only)          | 131  |  |

| SEC   | CTION 3                                          |      |  |

| Men   | nory Areas                                       | 133  |  |

| 3-1   | CQM1 Memory Area Functions                       | 134  |  |

| 3-2   | CPM1/CPM1A Memory Area Functions                 | 139  |  |

| 3-3   | SRM1 Memory Area Functions                       | 143  |  |

| 3-4   | SRM1 Flash Memory                                | 145  |  |

| 3-5   | Using Memory Cassettes (CQM1 Only)               | 146  |  |

| SEC   | CTION 4                                          |      |  |

| Lad   | der-diagram Programming                          | 151  |  |

| 4-1   | Basic Procedure                                  | 152  |  |

| 4-2   | Instruction Terminology                          | 152  |  |

| 4-3   | Basic Ladder Diagrams                            | 153  |  |

| 4-4   | Controlling Bit Status                           | 173  |  |

| 4-5   | Work Bits (Internal Relays)                      | 175  |  |

| 4-6   | Programming Precautions                          | 177  |  |

| 4-7   | Program Execution                                | 179  |  |

| SEC        | TION 5                                                                                               |

|------------|------------------------------------------------------------------------------------------------------|

|            | ruction Set                                                                                          |

| 5-1        | Notation                                                                                             |

| 5-2        | Instruction Format                                                                                   |

| 5-3        | Data Areas, Definer Values, and Flags                                                                |

| 5-4        | Differentiated Instructions                                                                          |

| 5-5        | Coding Right-hand Instructions                                                                       |

| 5-6        | Instruction Tables                                                                                   |

| 5-7        | Ladder Diagram Instructions                                                                          |

| 5-8        | Bit Control Instructions                                                                             |

| 5-9        | NO OPERATION – NOP(00)                                                                               |

|            | END – END(01)                                                                                        |

| 5-11       | INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03)                                                   |

| 5-12       | JUMP and JUMP END – JMP(04) and JME(05)                                                              |

| 5-13       | User Error Instructions:<br>FAILURE ALARM AND RESET – FAL(06) and<br>SEVERE FAILURE ALARM – FALS(07) |

| 5-14       | Step Instructions:                                                                                   |

|            | STEP DEFINE and STEP START–STEP(08)/SNXT(09)                                                         |

| 5-15       | Timer and Counter Instructions                                                                       |

| 5-16       | Shift Instructions                                                                                   |

| 5-17       | Data Movement Instructions                                                                           |

| 5-18       | Comparison Instructions                                                                              |

| 5-19       | Conversion Instructions                                                                              |

| 5-20       | BCD Calculation Instructions                                                                         |

|            | Binary Calculation Instructions                                                                      |

| 5-22       | Special Math Instructions                                                                            |

| 5-23       | Logic Instructions                                                                                   |

|            | Increment/Decrement Instructions                                                                     |

| 5-25       | Subroutine Instructions                                                                              |

|            | Special Instructions                                                                                 |

| 5-27       | Communications Instructions                                                                          |

| 5-28       | Advanced I/O Instructions                                                                            |

|            | TION 6                                                                                               |

|            | Link Commands                                                                                        |

|            |                                                                                                      |

| 6-1        | Communications Procedure                                                                             |

|            | Command and Response Formats                                                                         |

| 6-3        | Host Link Commands                                                                                   |

| SEC        | TION 7                                                                                               |

| PC (       | <b>Operations and Processing Time</b>                                                                |

| 7-1        | CQM1 Cycle Time and I/O Response Time                                                                |

| 7-1        | CPM1/CPM1A Cycle Time and I/O Response Time                                                          |

| 7-2<br>7-3 | SRM1 Cycle Time and I/O Response Time                                                                |

|            | • •                                                                                                  |

| SEC        | TION 8                                                                                               |

| Trou       | bleshooting                                                                                          |

| 8-1        | Introduction                                                                                         |

| 8-1        | Programming Console Operation Errors                                                                 |

| 8-2<br>8-3 |                                                                                                      |

| 8-3<br>8-4 | Programming Errors                                                                                   |

| 8-4<br>8-5 |                                                                                                      |

| 8-5<br>8-6 | Operating Errors                                                                                     |

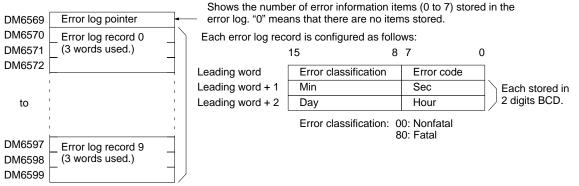

| 8-0<br>8-7 | Error Log                                                                                            |

|            |                                                                                                      |

| 8-8        | Troubleshooting Flowcharts                                                                           |

### Appendices

| A Programming Instructions                   | 441        |

|----------------------------------------------|------------|

| B Error and Arithmetic Flag Operation        | 447        |

| C Memory Areas                               | 451        |

| D Using the Clock Function                   | 469        |

| E I/O Assignment Sheet                       | 471        |

| F Program Coding Sheet                       | 473        |

| G List of FAL Numbers                        | 477        |

| H Extended ASCII                             | 479        |

| I CPM1/CPM1A and CQM1 Memory Area Comparison | 481        |

| Glossary                                     | 483        |

| Index                                        | <b>499</b> |

| Revision History                             | 507        |

### PRECAUTIONS

This section provides general precautions for using the Programmable Controller (PC) and related devices.

The information contained in this section is important for the safe and reliable application of the Programmable Controller. You must read this section and understand the information contained before attempting to set up or operate a PC system.

| 1 Intended Audience       | xiv |

|---------------------------|-----|

| 2 General Precautions     | xiv |

| 3 Safety Precautions      | xiv |

| 4 Application Precautions | xiv |

### 1 Intended Audience

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

- Personnel in charge of installing FA systems.

- Personnel in charge of designing FA systems.

- Personnel in charge of managing FA systems and facilities.

#### 2 General Precautions

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that may have a serious influence on lives and property if used improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are sufficient for the systems, machines, and equipment, and be sure to provide the systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the Unit. Be sure to read this manual before attempting to use the Unit and keep this manual close at hand for reference during operation.

**WARNING** It is extremely important that a PC and all PC Units be used for the specified purpose and under the specified conditions, especially in applications that can directly or indirectly affect human life. You must consult with your OMRON representative before applying a PC System to the above-mentioned applications.

#### 3 Safety Precautions

**Caution** Execute online edit only after confirming that no adverse effects will be caused by extending the cycle time. Otherwise, the input signals may not be readable.

**Caution** Confirm safety at the destination node before transferring a program to another node or changing the I/O memory area. Doing either of these without confirming safety may result in injury.

### 4 Application Precautions

Observe the following precautions when using the PC System.

**Caution** Failure to abide by the following precautions could lead to faulty operation of the PC or the system, or could damage the PC or PC Units. Always heed these precautions.

- Fail-safe measures must be taken by the customer to ensure safety in the event of incorrect, missing, or abnormal signals caused by broken signal lines, momentary power interruptions, or other causes.

- Interlock circuits, limit circuits, and similar safety measures in external circuits (i.e., not in the Programmable Controller) must be provided by the customer.

- Check the user program for proper execution before actually running it on the Unit. Not checking the program may result in an unexpected operation.

- Confirm that no adverse effect will occur in the system before attempting any of the following. Not doing so may result in an unexpected operation.

- Changing the operating mode of the PC.

- Force-setting/force-resetting any bit in memory.

- Changing the present value of any word or any set value in memory.

- Resume operation only after transferring to the new CPU Unit the contents of the DM and HR Areas required for resuming operation. Not doing so may result in an unexpected operation.

- Do not place objects on top of the cables. Doing so may break the cables.

- Before touching the Unit, be sure to first touch a grounded metallic object in order to discharge any static built-up. Not doing so may result in malfunction or damage.

- Do not touch the Expansion I/O Unit Connecting Cable while the power is being supplied in order to prevent any malfunction due to static electricity.

- **Caution** Always clear memory before beginning to program the CPM1, CPM1A or SRM1. Although memory is cleared before the CPU Unit is shipped (except for bits with specific functions), AR 1314, which turns ON when the internal capacitor cannot back up memory, may have turned ON during shipment.

- **Caution** If the CPM1 or CPM1A will be turned OFF for periods exceeding the data backup period of the internal capacitor, design the system so that it will not be influenced if data in the DM, HR, and CNT areas is cleared when power is turned OFF.

- **Caution** Either switch the CPM1 or CPM1A to RUN or MONITOR mode, or turn OFF and ON power to the CPM1 or CPM1A after changing from a Programming Device any data that is backed up in flash memory. This data includes the user program, read-only DM area (DM 6144 to DM 6599), and the PC Setup (DM 6600 to DM 6655).

- The user program and memory area data in the CPM1 or CPM1A are backed up either by an internal capacitor or in flash memory as shown in the following table.

| Backup method      | Data                                                          |

|--------------------|---------------------------------------------------------------|

| Internal capacitor | Read/write DM area (DM 0000 to DM 0999, DM 1022, and DM 1023) |

|                    | Error log area (DM 1000 to DM 1021)                           |

|                    | HR area (HR 00 to HR 19)                                      |

|                    | Counter area (CNT 000 to CNT 127)                             |

| Flash memory       | User program                                                  |

|                    | Read-only DM area (DM 6144 to DM 6599)                        |

|                    | PC Setup (DM 6600 to DM 6655)                                 |

- Note 1. The IR, TR, LR, and timer areas are not normally backed up when power is turned OFF and all contents will be cleared the next time power is turned ON. (The PC Setup setting in DM 6601 can be used to back up this data. Refer to details on the PC Setup later in this manual for details.)

- 2. The bits in the AR and SR areas have special functions and are set according to these functions when power is turned ON.

The capacitor backup time depends on the ambient temperature, as shown in the following graph. The backup time, however, assumes that the capacitor is fully charged, which requires that power be supplied to the CPU Unit continuously for at least 15 minutes.

If the power remains OFF for a period exceeding the data backup period, AR 1314 will turn ON to indicate that the capacitor can no longer back up data and the data backed up by the capacitor will be cleared. AR 1314 will remain ON unless it is turned OFF using I/O monitor operations, using memory clear operations, or from the user program.

If desired, the PC Setup setting in DM 6604 can be set to create a fatal error and thus stop the system when AR 1314 goes ON.

- The data stored in flash memory will not be lost even if power remains OFF for a period exceeding the data backup period, because the data stored in flash memory will be read to the CPU Unit when the CPM1 or CPM1A is turned ON.

- If the power is turned OFF without changing the mode from PROGRAM mode to RUN or MONITOR mode after having made changes in the data that is backed up in flash memory, the changes will not be written to flash memory. If the power is then left OFF for more than 20 days (at 25°C), the changes (i.e., the contents of the RAM) will be erased and the data values will become undefined.

- (!) Caution Be sure that the SRM1 system is not influenced by any undefined data if the data in the DM, HR, or CNT area is cleared when the SRM1 has been turned OFF for a period exceeding the data backup period of the internal lithium battery. If the AR 1414 flag is ON, the data will be held unless it is turned OFF using the I/O Monitor operation, instructions, etc. The system can be stopped by designating DM 6604 in the PC Setup so that a memory error occurs when the power interruption hold area is not held (with AR 1314 ON)

- A lithium battery in the CPU Unit is used to back up the counter values and the contents of the DM area, and HR area. The deterioration of the lithium battery capacity depends on the ambient temperature. The standard service life is 12 years at an ambient temperature of 40°C when operating 8 hours a day.

If the power remains off for a period exceeding the data backup period, the contents of the Data Memory (DM), Hold Relay (HR), and Counter (CNT) Areas in the CPU Unit may be cleared and the AR 1314 flag (which turns ON when the power interruption hold area is not held) may turn ON.

If the contents of the CPU Unit's program area are lost, the program stored in flash memory will be read to the CPU Unit's program area when the SRM1 is started up because the contents in the read-only area (DM 6144 through DM 6599) and PC Setup (DM 6600 through DM 6655) will be written to flash memory.

However, if the power is turned OFF without changing the mode even if changes are made in the read-only DM area (DM 6144 through DM 6599), or PC Setup (DM 6600 through DM 6655) using a peripheral device, the contents of changes will not be written to flash memory. Although the data in these areas is backed up by the lithium battery, contents of changes will disappear if the service life of the lithium battery expires. In this case, programs in the flash memory will be automatically read into the user program memory.

The changes can be saved by switching the SRM1 to RUN or MONITOR mode or turning OFF and restarting the SRM1 soon after the changes are made.

### SECTION 1 PC Setup and Other Features

This section explains the PC Setup and other CQM1/CPM1A/SRM1 features, including interrupt processing and communications. The PC Setup can be used to control the operating parameters of the CQM1/CPM1A/SRM1. To change the PC Setup, refer to the *CQM1 Operation Manual*, *CPM1 Operation Manual*, *CPM1A Operation Manual* or *SRM1 Master Control Units Operation Manual* for Programming Console procedures. Refer to the *SSS Operation Manual*: *C-series PCs* for SSS procedures.

If you are not familiar with OMRON PCs or ladder diagram program, you can read *1-5 PC Setup* as an overview of the operating parameters available for the CQM1/CPM1/CPM1A/SRM1, but may then want to read *Section 3 Memory Areas*, *Section 4 Ladder-diagram Programming*, and related instructions in *Section 5 Instruction Set* before completing this section.

| 1-1 | PC Set  | tup                                                      | 3  |

|-----|---------|----------------------------------------------------------|----|

|     | 1-1-1   | Changing the PC Setup                                    | 3  |

|     | 1-1-2   | CQM1 PC Setup Settings                                   | 4  |

|     | 1-1-3   | CPM1/CPM1A PC Setup Settings                             | 9  |

|     | 1-1-4   | SRM1 PC Setup Settings                                   | 13 |

| 1-2 | Basic H | PC Operation and I/O Processes                           | 16 |

|     | 1-2-1   | Startup Mode                                             | 16 |

|     | 1-2-2   | Hold Bit Status                                          | 17 |

|     | 1-2-3   | Program Memory Write-protection (CPM1/CPM1A Only)        | 17 |

|     | 1-2-4   | RS-232C Port Servicing Time (CQM1/SRM1 Only)             | 18 |

|     | 1-2-5   | Peripheral Port Servicing Time                           | 18 |

|     | 1-2-6   | Cycle Time                                               | 18 |

|     | 1-2-7   | Input Time Constants                                     | 19 |

|     | 1-2-8   | High-speed Timers (CQM1 Only)                            | 20 |

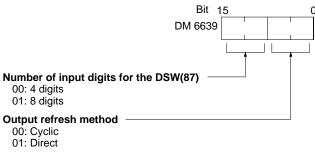

|     | 1-2-9   | DSW(87) Input Digits & Output Refresh Method (CQM1 Only) | 21 |

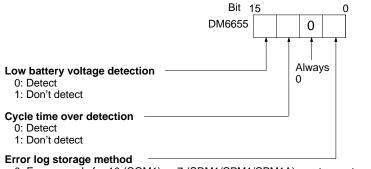

|     | 1-2-10  | Error Log Settings                                       | 21 |

| 1-3 | Pulse ( | Output Function (CQM1 Only)                              | 22 |

|     | 1-3-1   | Types of Pulse Outputs                                   | 22 |

|     | 1-3-2   | Standard Pulse Output from an Output Point               | 23 |

|     | 1-3-3   | Standard Pulse Output from Ports 1 and 2                 | 25 |

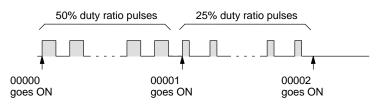

|     | 1-3-4   | Variable-duty-ratio Pulse Output from Ports 1 and 2      | 32 |

|     | 1-3-5   | Determining the Status of Ports 1 and 2                  | 34 |

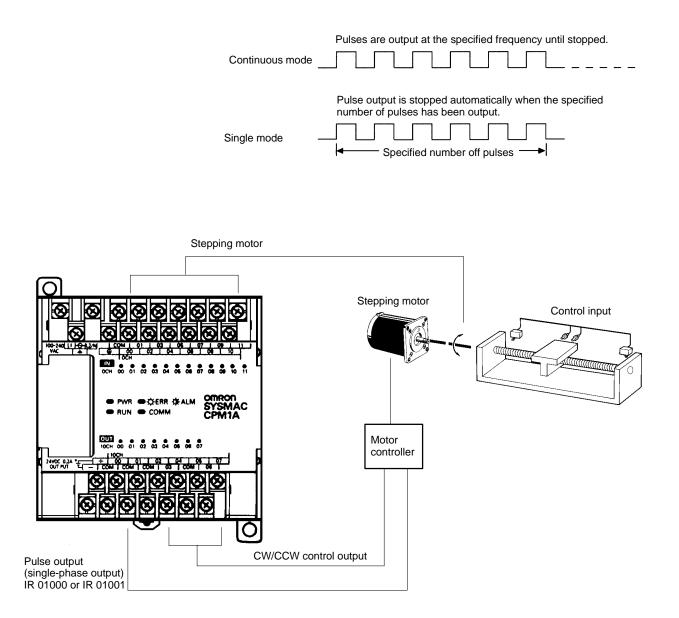

| 1-4 | Pulse ( | Output Function (CPM1A Only)                             | 35 |

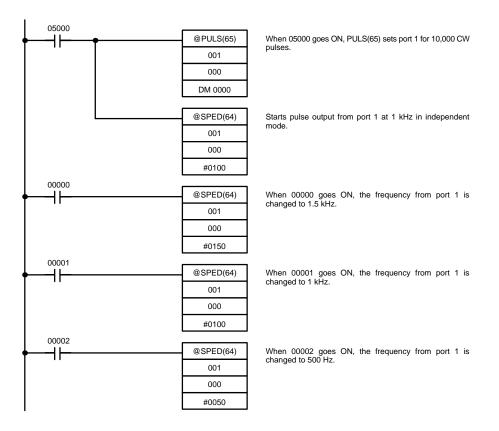

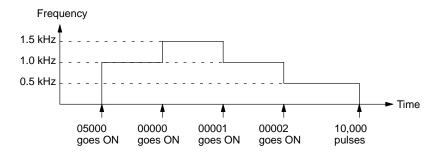

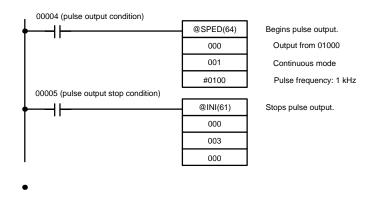

|     | 1-4-1   | Programming Example in Continuous Mode                   | 36 |

|     | 1-4-2   | Programming Example in Independent Mode                  | 36 |

|     | 1-4-3   | Using Pulse Output Instructions                          | 36 |

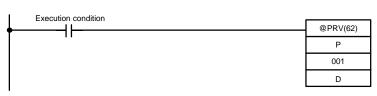

|     | 1-4-4   | Changing the Frequency                                   | 37 |

|     | 1-4-5   | Stopping Pulse Output                                    | 37 |

| 1-5 | CQM1    | Interrupt Functions                                      | 38 |

|     | 1-5-1   | Types of Interrupts                                      | 38 |

|     | 1-5-2   | Input Interrupts                                         | 39 |

|     | 1-5-3   | Masking All Interrupts                                   | 44 |

|     | 1-5-4   | Interval Timer Interrupts                                | 44 |

|     | 1-5-5   | High-speed Counter 0 Interrupts                          | 47 |

|     | 1-5-6   | High-speed Counter 0 Overflows/Underflows                | 53 |

|     | 1-5-7   | High-speed Counter 1 and 2 Interrupts (CQM1-CPU43-EV1)   | 55 |

|     | 1-5-8   | Absolute High-speed Counter Interrupts (CQM1-CPU44-EV1)  | 62 |

| 1-6 | CPM1/   | /CPM1A Interrupt Functions                               | 67 |

|     | 1-6-1   | Types of Interrupts                                      | 67 |

|     | 1-6-2   | Input Interrupts                                         | 69 |

|     | 1-6-3   | Masking All Interrupts                                   | 73 |

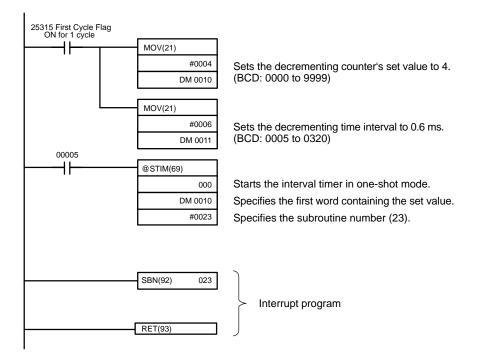

|     | 1-6-4   | Interval Timer Interrupts                                | 74 |

|     | 1-6-5   | High-speed Counter Interrupts                            | 76 |

| 1-7  | SRM1 I                              | Interrupt Functions                                    | 83  |

|------|-------------------------------------|--------------------------------------------------------|-----|

|      | 1-7-1                               | Types of Interrupts                                    | 83  |

|      | 1-7-2                               | Interval Timer Interrupts                              | 83  |

| 1-8  | Compol                              | Bus/S Distributed I/O Functions (SRM1 Only)            | 86  |

| 1-9  | Commu                               | inications Functions                                   | 87  |

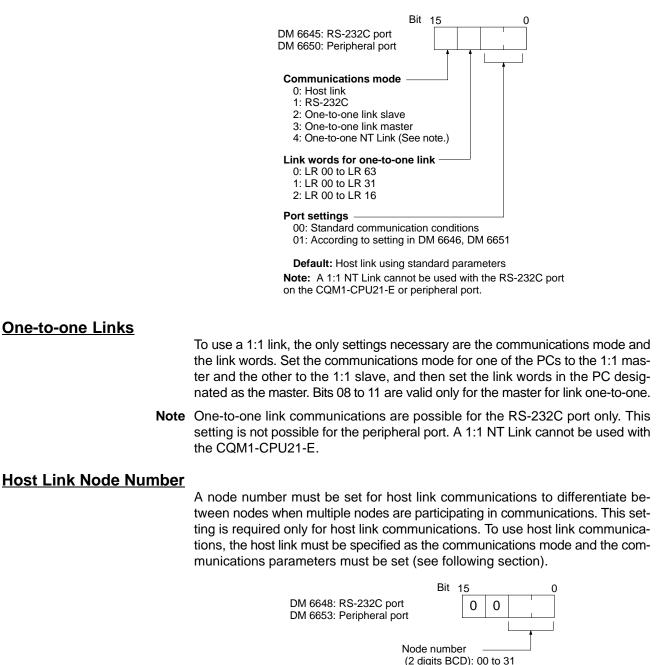

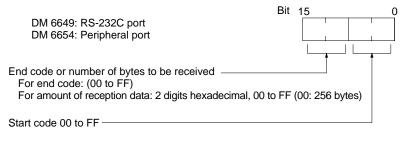

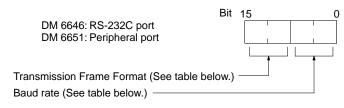

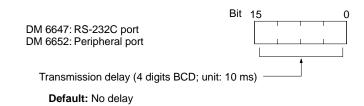

|      | 1-9-1                               | CQM1 PC Setup                                          | 88  |

|      | 1-9-2                               | Wiring Ports                                           | 91  |

|      | 1-9-3                               | CQM1 Host Link Communications                          | 91  |

|      | 1-9-4                               | CPM1/CPM1A Host Link Communications                    | 93  |

|      | 1-9-5                               | SRM1 Host Link Communications                          | 95  |

|      | 1-9-6                               | RS-232C Communications (CQM1/SRM1 Only)                | 98  |

|      | 1-9-7                               | CQM1 One-to-one Link Communications                    | 100 |

|      | 1-9-8                               | CPM1/CPM1A One-to-one Link Communications              | 101 |

|      | 1-9-9                               | CPM1/CPM1A NT Link Communications                      | 103 |

|      | 1-9-10                              | SRM1 One-to-one Link Communications                    | 104 |

|      | 1-9-11                              | SRM1 NT Link Communications                            | 106 |

|      | 1-9-12                              | SRM1 No Protocol Communications                        | 107 |

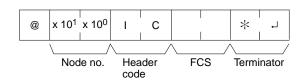

|      | 1-9-13                              | Transmission Data Configuration                        | 110 |

|      | 1-9-14                              | Transmission Flags                                     | 110 |

|      | 1-9-15                              | No Protocol Communications Program Example             | 111 |

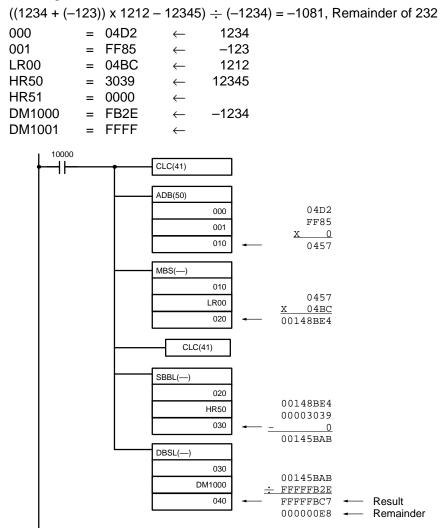

| 1-10 | Calculating with Signed Binary Data |                                                        | 111 |

|      | 1-10-1                              | Definition of Signed Binary Data                       | 112 |

|      | 1-10-2                              | Arithmetic Flags                                       | 113 |

|      | 1-10-3                              | Inputting Signed Binary Data Using Decimal Values      | 113 |

|      | 1-10-4                              | Using Signed-binary Expansion Instructions (CQM1 Only) | 113 |

|      | 1-10-5                              | Application Example Using Signed Binary Data           | 114 |

### 1-1 PC Setup

The PC Setup comprises various operating parameters that control CQM1/CPM1/CPM1A/SRM1 operation. In order to make the maximum use of CQM1/CPM1/CPM1A/SRM1 functionality when using interrupt processing and communications functions, the PC Setup may be customized according to operating conditions.

At the time of shipping, the defaults are set for general operating conditions, so that the CQM1/CPM1/CPM1A/SRM1 can be used without having to change the settings. You are, however, advised to check the default values before operation.

Default ValuesThe default values for the PC Setup are 0000 for all words. The default values<br/>can be reset at any time by turning ON SR 25210.

**Caution** When data memory (DM) is cleared from a Programming Device, the PC Setup settings will also be cleared to all zeros.

#### 1-1-1 Changing the PC Setup

PC Setup settings are accessed at various times depending on the setting, as described below.

- DM 6600 to DM 6614: Accessed only when PC's power supply is turned on.

- DM 6615 to DM 6644: Accessed only when program execution begins.

- DM 6645 to DM 6655: Accessed regularly when the power is on.

Since changes in the PC Setup become effective only at the times given above, the CQM1/CPM1/CPM1A/SRM1 will have to be restarted to make changes in DM 6600 to DM 6614 effective, and program execution will have to be restarted to make changes in DM 6615 to DM 6644 effective.

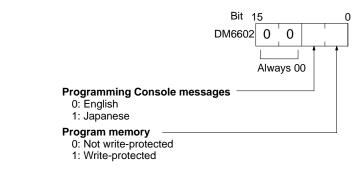

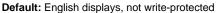

When DM 6602 bits 00 to 03 are set to protect the program memory, DM 6602 cannot be changed using the PC Setup operation of the Support Software. To change DM 6602, use the I/O Monitor or DM Edit operation.

Making Changes from a<br/>Peripheral DeviceThe PC Setup can be read, but not written into, from the user program. Writing<br/>can be done only by using a Programming Device.

Although the PC Setup is stored in DM 6600 to DM 6655, settings can be made and changed only from a Programming Device (e.g., SSS, or Programming Console). DM 6600 to DM 6644 can be set or changed only while in PROGRAM mode. DM 6645 to DM 6655 can be set or changed while in either PROGRAM mode or MONITOR mode.

The following settings can be made in PROGRAM mode from the SSS using menu operations. All other settings must be made using the hexadecimal setting operation.

- Startup Mode (DM 6600)

- I/O Hold Bit Status and Forced Status Hold Bit Status (DM 6601)

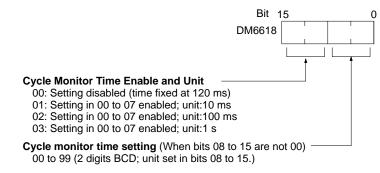

- Cycle Monitor Time (DM 6618)

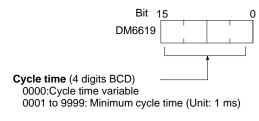

- Cycle Time (DM 6619)

- RS-232C Port Settings (DM 6645 to DM 6649)

- Note The RS-232C Port Settings (DM 6645 to DM 6649) are not used in CPM1/CPM1A PCs because these PCs aren't equipped with an RS-232C port.

#### **Errors in the PC Setup** If an incorrect PC Setup setting is accessed, a non-fatal error (error code 9B) will be generated, the corresponding error flag (AR 2400 to AR 2402 in the CQM1, AR 1300 to AR 1302 in the CPM1/CPM1A/SRM1) will be turned ON, and the default setting will be used instead of the incorrect setting.

#### 1-1-2 CQM1 PC Setup Settings

The PC Setup is broadly divided into four categories: 1) Settings related to basic CQM1 operation and I/O processes, 2) Settings related to pulse output functions, 3) Settings related to interrupts, and 4) Settings related to communications. This section will explain the settings according to these classifications.

The following table shows the setting in order in the DM area. For details, refer to the page numbers shown.

| Word(s)               | Bit(s)       | Function                                                                                                                                                                                       | Page   |

|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Startup Pro           | cessing (D   | M 6600 to DM 6614)                                                                                                                                                                             | L      |

| The following         | g settings a | re effective after transfer to the PC only after the PC is restarted.                                                                                                                          |        |

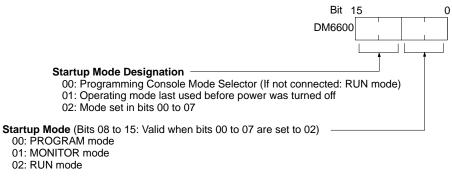

| DM 6600               | 00 to 07     | Startup mode (effective when bits 08 to 15 are set to 02).<br>00: PROGRAM; 01: MONITOR 02: RUN                                                                                                 | 16     |

|                       | 08 to 15     | Startup mode designation<br>00: Programming Console switch<br>01: Continue operating mode last used before power was turned off<br>02: Setting in 00 to 07                                     |        |

| DM 6601               | 00 to 07     | Not used.                                                                                                                                                                                      |        |

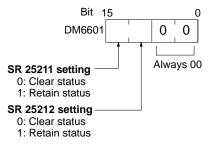

|                       | 08 to 11     | IOM Hold Bit (SR 25212) Status<br>0: Reset; 1: Maintain                                                                                                                                        | 17     |

|                       | 12 to 15     | Forced Status Hold Bit (SR 25211) Status<br>0: Reset; 1: Maintain                                                                                                                              |        |

| DM 6602 to<br>DM 6610 | 00 to 15     | Not used.                                                                                                                                                                                      |        |

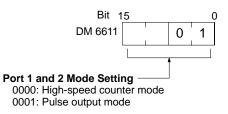

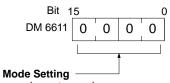

| DM 6611               | 00 to 15     | CQM1-CPU43-EV1: Mode setting for ports 1 and 2<br>0000: High-speed counter mode; 0001: Pulse output mode                                                                                       | 25, 63 |

|                       |              | CQM1-CPU44-EV1: Origin compensation setting for port 1 (4-digit BCD)                                                                                                                           |        |

| DM 6612               | 00 to 15     | CQM1-CPU44-EV1: Origin compensation setting for port 2 (4-digit BCD)                                                                                                                           | 63     |

| Pulse Outpu           | ut and Cyc   | le Time Settings (DM 6615 to DM 6619)                                                                                                                                                          |        |

| The following         | g settings a | re effective after transfer to the PC the next time operation is started.                                                                                                                      |        |

| DM 6615               | 00 to 07     | Word for pulse output.<br>00: IR 100; 01: IR101; 02: IR 102 15: IR 115                                                                                                                         | 23     |

|                       | 08 to 15     | Not used.                                                                                                                                                                                      |        |

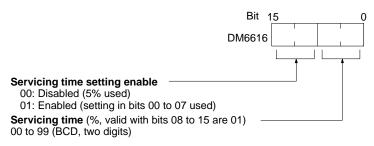

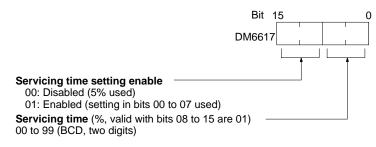

| DM 6616               | 00 to 07     | Servicing time for RS-232C port (effective when bits 08 to 15 are set to 01) 00 to 99 (BCD): Percentage of cycle time used to service RS-232C port.                                            | 18     |

|                       | 08 to 15     | RS-232C port servicing setting enable<br>00: 5% of the cycle time<br>01: Use time in 00 to 07.                                                                                                 |        |

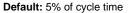

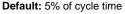

| DM 6617               | 00 to 07     | Servicing time for peripheral port (effective when bits 08 to 15 are set to 01) 00 to 99 (BCD): Percentage of cycle time used to service peripheral.                                           | 18     |

|                       | 08 to 15     | Peripheral port servicing setting enable<br>00: 5% of the cycle time<br>01: Use time in 00 to 07.                                                                                              |        |

| DM 6618               | 00 to 07     | Cycle monitor time (effective when bits 08 to 15 are set to 01, 02, or 03) 00 to 99 (BCD): Setting (see 08 to 15)                                                                              | 21     |

|                       | 08 to 15     | Cycle monitor enable (Setting in 00 to 07 x unit; 99 s max.)<br>00: 120 ms (setting in bits 00 to 07 disabled)<br>01: Setting unit: 10 ms<br>02: Setting unit: 100 ms<br>03: Setting unit: 1 s |        |

| DM 6619               | 00 to 15     | Cycle time<br>0000: Variable (no minimum)<br>0001 to 9999 (BCD): Minimum time in ms                                                                                                            | 18     |

| Word(s)       | Bit(s)      | Function                                                                                                                        | Page   |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|--------|

| -             |             | DM 6620 to DM 6639)                                                                                                             | _      |

| The following | settings ar | e effective after transfer to the PC the next time operation is started.                                                        |        |

| DM 6620       | 00 to 03    | Input constant for IR 00000 to IR 00007<br>0: 8 ms; 1: 1 ms; 2: 2 ms; 3: 4 ms; 4: 8 ms; 5: 16 ms; 6: 32 ms; 7: 64 ms; 8: 128 ms | 19     |

|               | 04 to 07    | Input constant for IR 00008 to IR 00015 (Setting same as bits 00 to 03)                                                         |        |

|               | 08 to 15    | Input constant for IR 001<br>00: 8 ms; 01: 1 ms; 02: 2 ms; 03: 4 ms; 04: 8 ms; 05: 16 ms; 06: 32 ms; 07: 64 ms; 08:<br>128 ms   |        |

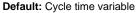

| DM 6621       | 00 to 07    | Input constant for IR 002 (Setting same as for IR 001.)                                                                         |        |

|               | 08 to 15    | Input constant for IR 003 (Setting same as for IR 001.)                                                                         | _      |

| DM 6622       | 00 to 07    | Input constant for IR 004 (Setting same as for IR 001.)                                                                         | _      |

|               | 08 to 15    | Input constant for IR 005 (Setting same as for IR 001.)                                                                         | _      |

| DM 6623       | 00 to 07    | Input constant for IR 006 (Setting same as for IR 001.)                                                                         |        |

|               | 08 to 15    | Input constant for IR 007 (Setting same as for IR 001.)                                                                         | _      |

| DM 6624       | 00 to 07    | Input constant for IR 008 (Setting same as for IR 001.)                                                                         | _      |

|               | 08 to 15    | Input constant for IR 009 (Setting same as for IR 001.)                                                                         | 4      |

| DM 6625       | 00 to 07    | Input constant for IR 010 (Setting same as for IR 001.)                                                                         | _      |

|               | 08 to 15    | Input constant for IR 011 (Setting same as for IR 001.)                                                                         | _      |

| DM 6626       | 00 to 07    | Input constant for IR 012 (Setting same as for IR 001.)                                                                         | _      |

|               | 08 to 15    | Input constant for IR 013 (Setting same as for IR 001.)                                                                         | _      |

| DM 6627       | 00 to 07    | Input constant for IR 014 (Setting same as for IR 001.)                                                                         | _      |

|               | 08 to 15    | Input constant for IR 015 (Setting same as for IR 001.)                                                                         |        |

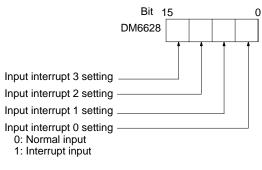

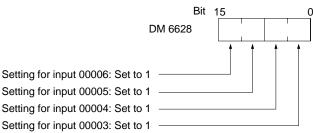

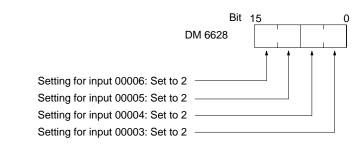

| DM 6628       | 00 to 03    | Interrupt enable for IR 00000 (0: Normal input; 1: Interrupt input)                                                             | 40     |

|               | 04 to 07    | Interrupt enable for IR 00001 (0: Normal input; 1: Interrupt input)                                                             |        |

|               | 08 to 11    | Interrupt enable for IR 00002 (0: Normal input; 1: Interrupt input)                                                             |        |

|               | 12 to 15    | Interrupt enable for IR 00003 (0: Normal input; 1: Interrupt input)                                                             |        |

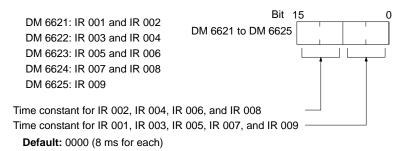

| DM 6629       | 00 to 07    | Number of high-speed timers for interrupt refreshing<br>00 to 15 (BCD; e.g., set 15 for 00 to 14)                               | 20     |

|               | 08 to 15    | High-speed timer interrupt refresh enable<br>00: 16 timers (setting in bits 00 to 07 disabled)<br>01: Use setting in 00 to 07   |        |

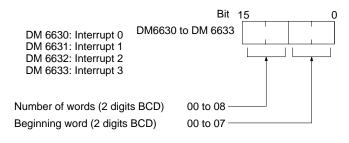

| DM 6630       | 00 to 07    | First input refresh word for I/O interrupt 0: 00 to 11 (BCD)                                                                    | 40     |

|               | 08 to 15    | Number of input refresh words for I/O interrupt 0: 00 to 12 (BCD)                                                               |        |

| DM 6631       | 00 to 07    | First input refresh word for I/O interrupt 1: 00 to 11 (BCD)                                                                    |        |

|               | 08 to 15    | Number of input refresh words for I/O interrupt 1: 00 to 12 (BCD)                                                               |        |

| DM 6632       | 00 to 07    | First input refresh word for I/O interrupt 2: 00 to 11 (BCD)                                                                    |        |

|               | 08 to 15    | Number of input refresh words for I/O interrupt 2: 00 to 12 (BCD)                                                               |        |

| DM 6633       | 00 to 07    | First input refresh word for I/O interrupt 3: 00 to 11 (BCD)                                                                    |        |

|               | 08 to 15    | Number of input refresh words for I/O interrupt 3: 00 to 12 (BCD)                                                               |        |

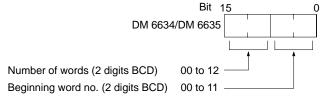

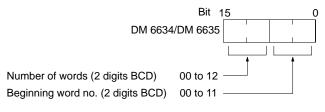

| DM 6634       | 00 to 07    | First input refresh word for high-speed counter 1: 00 to 11 (BCD)                                                               | 40     |

|               | 08 to 15    | Number of input refresh words for high-speed counter 1: 00 to 12 (BCD)                                                          |        |

| DM 6635       | 00 to 07    | First input refresh word for high-speed counter 1: 00 to 11 (BCD)                                                               | 40     |

|               | 08 to 15    | Number of input refresh words for high-speed counter 1: 00 to 12 (BCD)                                                          |        |

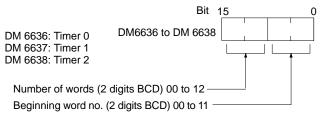

| DM 6636       | 00 to 07    | First input refresh word for interval timer 0: 00 to 07 (BCD)                                                                   | 45, 50 |

|               | 08 to 15    | Number of input refresh words for interval timer 0: 00 to 08 (BCD)                                                              | 1      |

| DM 6637       | 00 to 07    | First input refresh word for interval timer 1: 00 to 07 (BCD)                                                                   | 1      |

|               | 08 to 15    | Number of input refresh words for interval timer 1: 00 to 08 (BCD)                                                              | 1      |

| DM 6638       | 00 to 07    | First input refresh word for interval timer 2 (also used for high-speed counter 0): 00 to 07 (BCD)                              |        |

|               | 08 to 15    | Number of input refresh words for interval timer 2: 00 to 08 (BCD) (also used for high-speed counter 0)                         | 1      |

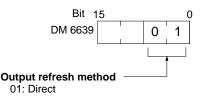

| Word(s)             | Bit(s)       | Function                                                                                                                    | Page       |

|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|------------|

| DM 6639             | 00 to 07     | Output refresh method<br>00: Cyclic; 01: Direct                                                                             | 21,<br>383 |

|                     | 08 to 15     | Number of digits for DIGITAL SWITCH (DSW(87)) instruction<br>00: 4 digits; 01: 8 digits                                     | 21,<br>122 |

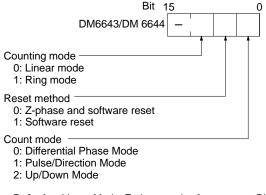

| High-speed          | Counter S    | ettings (DM 6640 to DM 6644)                                                                                                |            |

| The following       | g settings a | re effective after transfer to the PC the next time operation is started.                                                   |            |

| DM 6640,<br>DM 6641 | 00 to 15     | Not used.                                                                                                                   |            |

| DM 6642             | 00 to 03     | High-speed counter 0 mode<br>0: Up/down counter mode; 4: Incrementing counter mode                                          | 50         |

|                     | 04 to 07     | High-speed counter 0 reset mode<br>0: Z phase and software reset; 1: Software reset only                                    |            |

|                     | 08 to 15     | High-speed counter 0 enable<br>00: Don't use high-speed counter; 01: Use high-speed counter with settings in 00 to 07       |            |

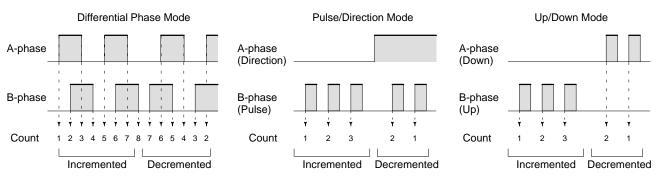

| DM 6643             | 00 to 03     | CQM1-CPU43-EV1: Port 1 input setting<br>0: Differential phase input; 1: Pulse/Direction input; 2: Up/Down input             | 55, 62     |

|                     |              | CQM1-CPU44-EV1: Port 1 input setting<br>0: 8-bit input; 1: 10-bit input; 2: 12-bit input                                    |            |

|                     | 04 to 07     | CQM1-CPU43-EV1: Port 1 reset setting<br>0: Z phase and software reset; 1: Software reset only                               | 57         |

|                     |              | CQM1-CPU44-EV1: Not used. Set to 0.                                                                                         |            |

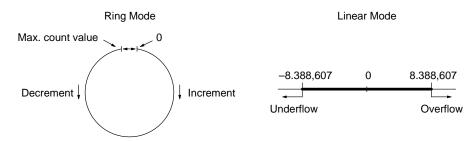

|                     | 08 to 11     | CQM1-CPU43-EV1: Port 1 counting mode setting<br>0: Linear mode; 1: Ring mode                                                | 55, 62     |

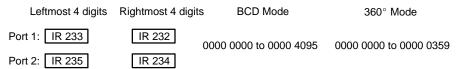

|                     |              | CQM1-CPU44-EV1: Port 1 mode setting<br>0: BCD mode; 1: 360° mode                                                            |            |

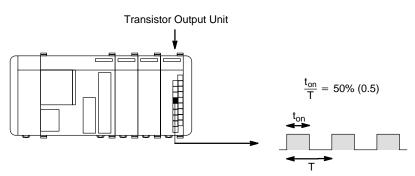

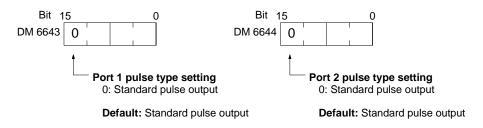

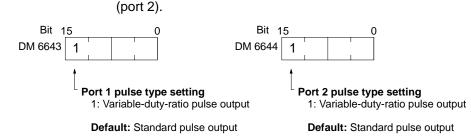

|                     | 12 to 15     | CQM1-CPU43-EV1: Port 1 pulse type setting<br>0: Standard pulse output (0.5 duty ratio); 1: Variable-duty-ratio pulse output | 25, 32     |

|                     |              | CQM1-CPU44-EV1: Not used. Set to 0.                                                                                         |            |

| DM 6644             | 00 to 15     | Port 2 settings (Identical to the port 1 settings in DM 6643.)                                                              |            |

| Word(s)       | Bit(s)               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                             |  |

|---------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|