# **DL06 User Manual**

Manual Number: D0-06USER-M

# Volume 2 of 2

# WARNING

Thank you for purchasing automation equipment from Automationdirect.com<sup>®</sup>, doing business as, AutomationDirect. We want your new automation equipment to operate safely. Anyone who installs or uses this equipment should read this publication (and any other relevant publications) before installing or operating the equipment.

To minimize the risk of potential safety problems, you should follow all applicable local and national codes that regulate the installation and operation of your equipment. These codes vary from area to area and usually change with time. It is your responsibility to determine which codes should be followed, and to verify that the equipment, installation, and operation is in compliance with the latest revision of these codes.

At a minimum, you should follow all applicable sections of the National Fire Code, National Electrical Code, and the codes of the National Electrical Manufacturer's Association (NEMA). There may be local regulatory or government offices that can also help determine which codes and standards are necessary for safe installation and operation.

Equipment damage or serious injury to personnel can result from the failure to follow all applicable codes and standards. We do not guarantee the products described in this publication are suitable for your particular application, nor do we assume any responsibility for your product design, installation, or operation.

Our products are not fault-tolerant and are not designed, manufactured or intended for use or resale as online control equipment in hazardous environments requiring fail-safe performance, such as in the operation of nuclear facilities, aircraft navigation or communication systems, air traffic control, direct life support machines, or weapons systems, in which the failure of the product could lead directly to death, personal injury, or severe physical or environmental damage ("High Risk Activities"). AutomationDirect specifically disclaims any expressed or implied warranty of fitness for High Risk Activities.

For additional warranty and safety information, see the Terms and Conditions section of our catalog. If you have any questions concerning the installation or operation of this equipment, or if you need additional information, please call us at 770-844-4200.

This publication is based on information that was available at the time it was printed. At **AutomationDirect** we constantly strive to improve our products and services, so we reserve the right to make changes to the products and/or publications at any time without notice and without any obligation. This publication may also discuss features that may not be available in certain revisions of the product.

### **Trademarks**

This publication may contain references to products produced and/or offered by other companies. The product and company names may be trademarked and are the sole property of their respective owners. **AutomationDirect** disclaims any proprietary interest in the marks and names of others.

### Copyright 2006, Automationdirect.com Incorporated All Rights Reserved

No part of this manual shall be copied, reproduced, or transmitted in any way without the prior, written consent of **Automationdirect.com Incorporated**. **AutomationDirect** retains the exclusive rights to all information included in this document.

# AVERTISSEMENT

Nous vous remercions d'avoir acheté l'équipement d'automatisation de **Automationdirect.comMC**, en faisant des affaires comme, **AutomationDirect**. Nous tenons à ce que votre nouvel équipement d'automatisation fonctionne en toute sécurité. Toute personne qui installe ou utilise cet équipement doit lire la présente publication (et toutes les autres publications pertinentes) avant de l'installer ou de l'utiliser.

Afin de réduire au minimum le risque d'éventuels problèmes de sécurité, vous devez respecter tous les codes locaux et nationaux applicables régissant l'installation et le fonctionnement de votre équipement. Ces codes diffèrent d'une région à l'autre et, habituellement, évoluent au fil du temps. Il vous incombe de déterminer les codes à respecter et de vous assurer que l'équipement, l'installation et le fonctionnement sont conformes aux exigences de la version la plus récente de ces codes.

Vous devez, à tout le moins, respecter toutes les sections applicables du Code national de prévention des incendies, du Code national de l'électricité et des codes de la National Electrical Manufacturer's Association (NEMA). Des organismes de réglementation ou des services gouvernementaux locaux peuvent également vous aider à déterminer les codes ainsi que les normes à respecter pour assurer une installation et un fonctionnement sûrs.

L'omission de respecter la totalité des codes et des normes applicables peut entraîner des dommages à l'équipement ou causer de graves blessures au personnel. Nous ne garantissons pas que les produits décrits dans cette publication conviennent à votre application particulière et nous n'assumons aucune responsabilité à l'égard de la conception, de l'installation ou du fonctionnement de votre produit.

Nos produits ne sont pas insensibles aux défaillances et ne sont ni conçus ni fabriqués pour l'utilisation ou la revente en tant qu'équipement de commande en ligne dans des environnements dangereux nécessitant une sécurité absolue, par exemple, l'exploitation d'installations nucléaires, les systèmes de navigation aérienne ou de communication, le contrôle de la circulation aérienne, les équipements de survie ou les systèmes d'armes, pour lesquels la défaillance du produit peut provoquer la mort, des blessures corporelles ou de graves dommages matériels ou environnementaux («activités à risque élevé»). La société **AutomationDirect** nie toute garantie expresse ou implicite d'aptitude à l'emploi en ce qui a trait aux activités à risque élevé.

Pour des renseignements additionnels touchant la garantie et la sécurité, veuillez consulter la section Modalités et conditions de notre documentation. Si vous avez des questions au sujet de l'installation ou du fonctionnement de cet équipement, ou encore si vous avez besoin de renseignements supplémentaires, n'hésitez pas à nous téléphoner au 770-844-4200.

Cette publication s'appuie sur l'information qui était disponible au moment de l'impression. À la société **AutomationDirect**, nous nous efforçons constamment d'améliorer nos produits et services. C'est pourquoi nous nous réservons le droit d'apporter des modifications aux produits ou aux publications en tout temps, sans préavis ni quelque obligation que ce soit. La présente publication peut aussi porter sur des caractéristiques susceptibles de ne pas être offertes dans certaines versions révisées du produit.

# Marques de commerce

La présente publication peut contenir des références à des produits fabriqués ou offerts par d'autres entreprises. Les désignations des produits et des entreprises peuvent être des marques de commerce et appartiennent exclusivement à leurs propriétaires respectifs. **AutomationDirect** nie tout intérêt dans les autres marques et désignations.

# Copyright 2006, Automationdirect.com Incorporated Tous droits réservés

Nulle partie de ce manuel ne doit être copiée, reproduite ou transmise de quelque façon que ce soit sans le consentement préalable écrit de la société **Automationdirect.com Incorporated**. **AutomationDirect** conserve les droits exclusifs à l'égard de tous les renseignements contenus dans le présent document.

# VOLUME ONE: TABLE OF CONTENTS

# **Chapter 1: Getting Started**

| Introduction  The Purpose of this Manual  Supplemental Manuals  Technical Support                          |      |

|------------------------------------------------------------------------------------------------------------|------|

| Conventions Used                                                                                           |      |

| DL06 Micro PLC Overview  The DL06 PLC Features  DirectSOFT 5 Programming for Windows™  Handheld Programmer |      |

| I/O Quick Selection Guide                                                                                  | 1–5  |

| Quick Start                                                                                                | 1–6  |

| Steps to Designing a Successful System                                                                     | 1–10 |

| Questions and Answers about DL06 Micro PLCs                                                                |      |

| Chapter 2: Installation, Wiring, and Specifications                                                        |      |

| Safety Guidelines                                                                                          |      |

| Plan for Safety                                                                                            |      |

| Three Levels of Protection                                                                                 |      |

| Emergency Stops                                                                                            |      |

| Emergency Power Disconnect                                                                                 |      |

| Orderly System Shutdown                                                                                    |      |

| Class 1, Division 2 Approval                                                                               |      |

| Orientation to DL06 Front Panel                                                                            |      |

| Terminal Block Removal                                                                                     |      |

| Mounting Guidelines                              |     | <b>-7</b> |

|--------------------------------------------------|-----|-----------|

| Unit Dimensions                                  |     | -7        |

| Enclosures                                       |     | -7        |

| Panel Layout & Clearances                        |     | -8        |

| Using Mounting Rails                             |     | -9        |

| Environmental Specifications                     |     | 10        |

| Agency Approvals                                 |     | 10        |

| Marine Use                                       |     | 10        |

| Wiring Guidelines                                |     | 11        |

| Fuse Protection for Input Power                  |     |           |

| External Power Source                            |     |           |

| Planning the Wiring Routes                       |     |           |

| Fuse Protection for Input and Output Circuits    |     |           |

| I/O Point Numbering                              |     |           |

| System Wiring Strategies                         |     | 14        |

| PLC Isolation Boundaries                         |     |           |

| Connecting Operator Interface Devices            |     | 15        |

| Connecting Programming Devices                   |     |           |

| Sinking / Sourcing Concepts                      |     | 16        |

| I/O "Common" Terminal Concepts                   |     | 17        |

| Connecting DC I/O to "Solid State" Field Devices |     | 18        |

| Solid State Input Sensors                        |     | 18        |

| Solid State Output Loads                         |     | 18        |

| Relay Output Wiring Methods                      |     | 20        |

| Surge Suppression For Inductive Loads            |     | 21        |

| Prolonging Relay Contact Life                    |     | 22        |

| DC Input Wiring Methods                          |     | 23        |

| DC Output Wiring Methods                         |     | 24        |

| High-Speed I/O Wiring Methods                    |     | 25        |

| Wiring Diagrams and Specifications               |     | 26        |

| D0–06AA I/O Wiring Diagram                       |     | 26        |

| D0–06AR I/O Wiring Diagram                       |     | 28        |

| D0–06DA I/O Wiring Diagram                       |     | 30        |

| D0-06DD1 I/O Wiring Diagram                      | 2-3 | 32        |

| D0–06DD2 I/O Wiring Diagram                      | 2-3 | 34        |

| D0-06DR I/O Wiring Diagram                       | 2-3 | 36        |

| D0-06DD1-D I/O Wiring Diagram                    | 2_3 | 38        |

| D0–06DD2–D I/O Wiring Diagram                                                                                                                                                                                                                                                              |                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Glossary of Specification Terms                                                                                                                                                                                                                                                            | 2–44                                                                 |

| Chapter 3: CPU Specifications and Operation                                                                                                                                                                                                                                                |                                                                      |

| Introduction                                                                                                                                                                                                                                                                               |                                                                      |

| CPU Specifications                                                                                                                                                                                                                                                                         |                                                                      |

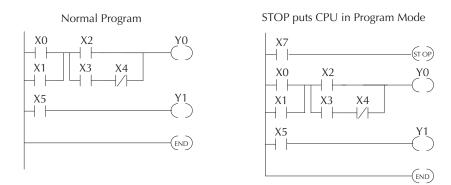

| CPU Hardware Setup  Communication Port Pinout Diagrams  Connecting the Programming Devices  CPU Setup Information  Status Indicators  Mode Switch Functions  Changing Modes in the DL06 PLC  Mode of Operation at Power-up                                                                 | 3–4<br>3–5<br>3–5<br>3–6<br>3–7<br>3–7                               |

| Using Battery Backup  Battery Backup  Auxiliary Functions  Clearing an Existing Program  Initializing System Memory  Setting Retentive Memory Ranges  Using a Password                                                                                                                     | 3–8<br>3–9<br>3–9<br>3–10                                            |

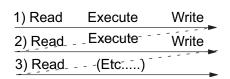

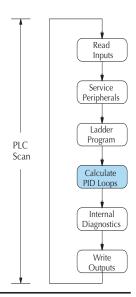

| CPU Operation  CPU Operating System  Program Mode  Run Mode  Read Inputs  Service Peripherals and Force I/O  CPU Bus Communication  Update Clock, Special Relays and Special Registers  Solve Application Program  Solve PID Loop Equations  Write Outputs  Write Outputs to Specialty I/O | 3-12<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-15<br>3-16<br>3-16 |

| Diagnostics                                                                                                                                                                                                                                                                                |                                                                      |

| I/O Response Time                                              |

|----------------------------------------------------------------|

| Is Timing Important for Your Application?3–17                  |

| Normal Minimum I/O Response                                    |

| Normal Maximum I/O Response3–18                                |

| Improving Response Time3–19                                    |

| CPU Scan Time Considerations3–20                               |

| Reading Inputs                                                 |

| Writing Outputs                                                |

| Service Peripherals                                            |

| CPU Bus Communication                                          |

| Update Clock/Calendar, Special Relays, Special Registers3–21   |

| Application Program Execution                                  |

| PLC Numbering Systems                                          |

| PLC Resources                                                  |

| V–Memory                                                       |

| Binary-Coded Decimal Numbers                                   |

| Hexadecimal Numbers                                            |

| Memory Map                                                     |

| Octal Numbering System3–25                                     |

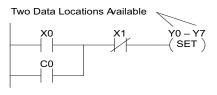

| Discrete and Word Locations                                    |

| V-memory Locations for Discrete Memory Areas                   |

| Input Points (X Data Type)3–26                                 |

| Output Points (Y Data Type)                                    |

| Control Relays (C Data Type)3–26                               |

| Timers and Timer Status Bits (T Data Type)3–26                 |

| Timer Current Values (V Data Type)3–27                         |

| Counters and Counter Status Bits (CT Data type)                |

| Counter Current Values (V Data Type)                           |

| Word Memory (V Data Type)3–28                                  |

| Stages (S Data type)                                           |

| Special Relays (SP Data Type)3–28                              |

| DL06 System V-memory3–29                                       |

| System Parameters and Default Data Locations (V Data Type)3-29 |

| DL06 Aliases                                                   |

| DL06 Memory Map                                                |

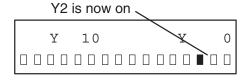

| X Input/Y Output Bit Map                                       |

| Stage Control/Status Bit Map                             | 3–34 |

|----------------------------------------------------------|------|

| Control Relay Bit Map                                    | 3–36 |

| Timer Status Bit Map                                     | 3–38 |

| Counter Status Bit Map                                   |      |

| GX and GY I/O Bit Map                                    |      |

|                                                          |      |

| Chapter 4: System Design and Configuration               |      |

| DL06 System Design Strategies                            | 4–2  |

| I/O System Configurations                                |      |

| Networking Configurations                                | 4–2  |

| Module Placement                                         | 4–3  |

| Slot Numbering                                           |      |

| Automatic I/O Configuration                              |      |

| Manual I/O Configuration                                 |      |

| Power Budgeting                                          |      |

| Power supplied                                           |      |

| Power required by option cards                           |      |

| Configuring the DL06's Comm Ports                        |      |

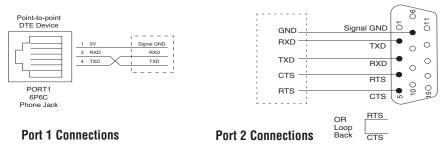

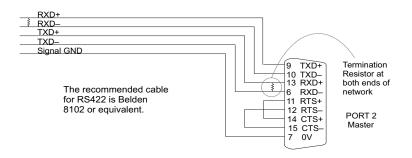

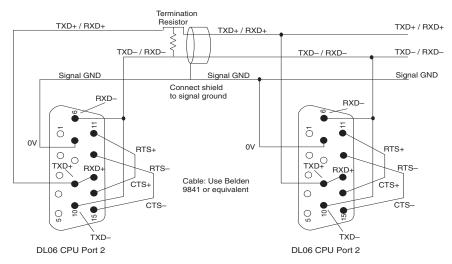

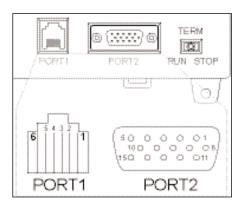

| DL06 Port Specifications                                 |      |

| DL06 Port Pinouts                                        |      |

| Choosing a Network Specification                         |      |

| RS-232 Network                                           |      |

| RS-422 Network                                           |      |

|                                                          |      |

| Connecting to MODBUS and DirectNET Networks              |      |

| DirectNET Port Configuration                             |      |

| Non–Sequence Protocol (ASCII In/Out and PRINT)           |      |

| Non-Sequence Port Configuration                          |      |

| Network Slave Operation                                  | 4–12 |

| MODBUS Function Codes Supported                          |      |

| Determining the MODBUS Address                           |      |

| If Your Host Software Requires the Data Type and Address | 4–13 |

| Example 1: V2100                                          | 4–14 |

|-----------------------------------------------------------|------|

| Example 2: Y20                                            | 4–14 |

| Example 3: T10 Current Value                              | 4–14 |

| Example 4: C54                                            | 4–14 |

| If Your MODBUS Host Software Requires an Address ONLY     | 4–15 |

| Example 1: V2100 584/984 Mode                             | 4–17 |

| Example 2: Y20 584/984 Mode                               | 4–17 |

| Example 3: T10 Current Value 484 Mode                     | 4–17 |

| Example 4: C54 584/984 Mode                               | 4–17 |

| Network Master Operation                                  | 4–18 |

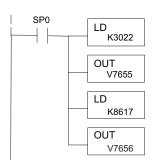

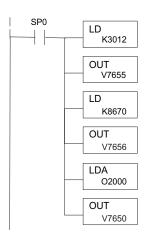

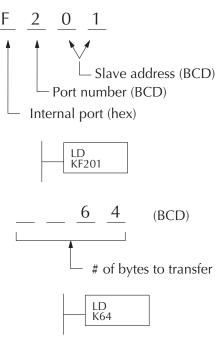

| Step 1: Identify Master Port # and Slave #                |      |

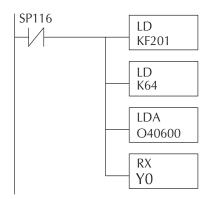

| Step 2: Load Number of Bytes to Transfer                  |      |

| Step 3: Specify Master Memory Area                        |      |

| Step 4: Specify Slave Memory Area                         |      |

| Communications from a Ladder Program                      |      |

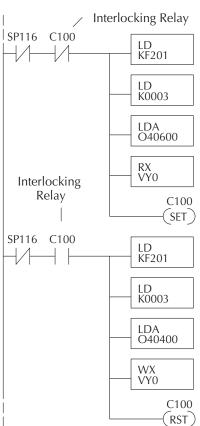

| Multiple Read and Write Interlocks                        |      |

| Network Master Operation (using MRX and MWX Instructions) | 4–22 |

| MODBUS Function Codes Supported                           |      |

| MODBUS Read from Network(MRX)                             |      |

| MRX Slave Memory Address                                  |      |

| MRX Master Memory Addresses                               |      |

| MRX Number of Elements                                    |      |

| MRX Exception Response Buffer                             |      |

| MODBUS Write to Network (MWX)                             |      |

| MWX Slave Memory Address                                  |      |

| MWX Master Memory Addresses                               |      |

| MWX Number of Elements                                    |      |

| MWX Exception Response Buffer                             | 4–26 |

| MRX/MWX Example in DirectSOFT 5                           |      |

| Multiple Read and Write Interlocks                        |      |

| Chantau F. Standaud DII Instructions                      |      |

| Chapter 5: Standard RLL Instructions                      |      |

| Introduction                                              |      |

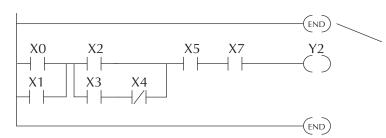

| Using Boolean Instructions                                |      |

| END Statement                                             |      |

| Simple Rungs                                              | 5-5  |

| Normally Closed Contact                               | 5–6   |

|-------------------------------------------------------|-------|

| Contacts in Series                                    |       |

| Midline Outputs                                       |       |

| Parallel Elements                                     |       |

| Joining Series Branches in Parallel                   |       |

| Joining Parallel Branches in Series                   |       |

| Combination Networks                                  |       |

| Comparative Boolean                                   |       |

| Boolean Stack                                         |       |

| Immediate Boolean                                     | 5–9   |

| Boolean Instructions                                  | 5–10  |

| Comparative Boolean                                   | 5–26  |

| Immediate Instructions                                | 5–32  |

| Timer, Counter and Shift Register Instructions        | 5–39  |

| Using Timers                                          | 5–39  |

| Timer Example Using Discrete Status Bits              | 5–41  |

| Timer Example Using Comparative Contacts              | 5–41  |

| Accumulating Timer Example using Discrete Status Bits | 5–43  |

| Accumulator Timer Example Using Comparative Contacts  | 5–43  |

| Using Counters                                        |       |

| Counter Example Using Discrete Status Bits            |       |

| Counter Example Using Comparative Contacts            |       |

| Stage Counter Example Using Discrete Status Bits      |       |

| Stage Counter Example Using Comparative Contacts      |       |

| Up / Down Counter Example Using Discrete Status Bits  |       |

| Up / Down Counter Example Using Comparative Contacts  | 5–50  |

| Accumulator/Stack Load and Output Data Instructions   | 5–52  |

| Using the Accumulator                                 |       |

| Copying Data to the Accumulator                       |       |

| Changing the Accumulator Data                         |       |

| Using the Accumulator Stack                           |       |

| Using Pointers                                        | 5–55  |

| Logical Instructions (Accumulator)                    |       |

| Math Instructions                                     | 5–86  |

| Transcandantal Eurotions                              | 5 110 |

| Bit Operation Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number Conversion Instructions (Accumulator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clock/Calendar Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CPU Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Program Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Message Instructions.5–186Move Block Instruction (MOVBLK).5–189Copy Data From a Data Label Area to V-memory.5–189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Intelligent I/O Instructions.5–194Read from Intelligent Module (RD).5–194Write to Intelligent Module (WT).5–195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Network Instructions.5–196Direct Text Entry.5–200Embedding date and/or time variables.5–201Embedding V-memory data.5–201Data Format Suffixes for Embedded V-memory Data.5–202Text Entry from V-memory.5–203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MODBUS RTU Instructions.5–204MRX Slave Address Ranges.5–205MWX Slave Address Ranges.5–208MWX Master Memory Address Ranges.5–208MWX Number of Elements.5–208MWX Exception Response Buffer.5–208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

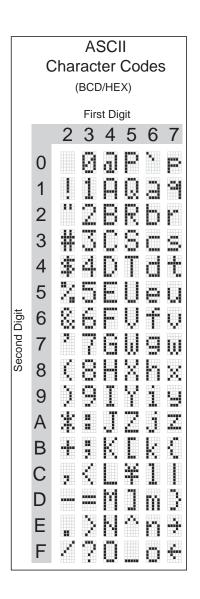

| ASCII Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The might be an (150n) in the decivity in the transfer of the |

# VOLUME TWO: TABLE OF CONTENTS

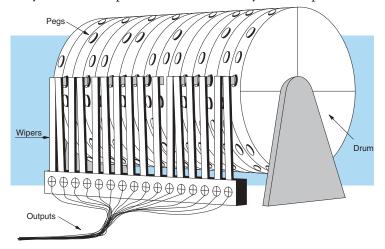

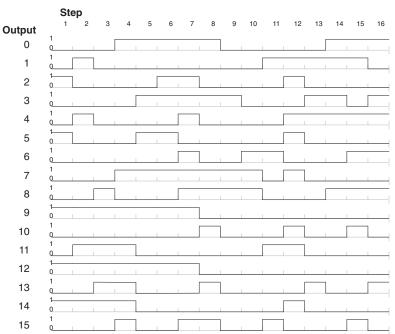

## **Chapter 6: Drum Instruction Programming**

| Introduction                               |

|--------------------------------------------|

| Purpose                                    |

| Drum Terminology                           |

| Drum Chart Representation                  |

| Output Sequences                           |

| Step Transitions                           |

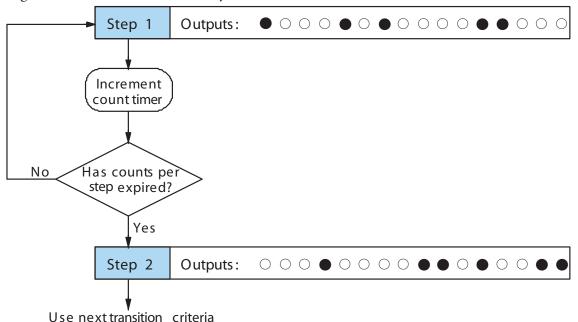

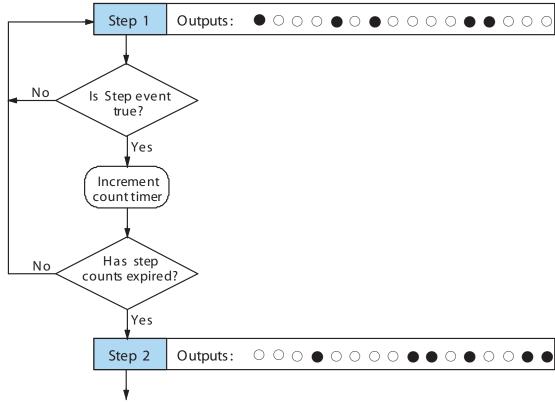

| Drum Instruction Types6-                   |

| Timer-Only Transitions                     |

| Timer and Event Transitions                |

| Event-Only Transitions                     |

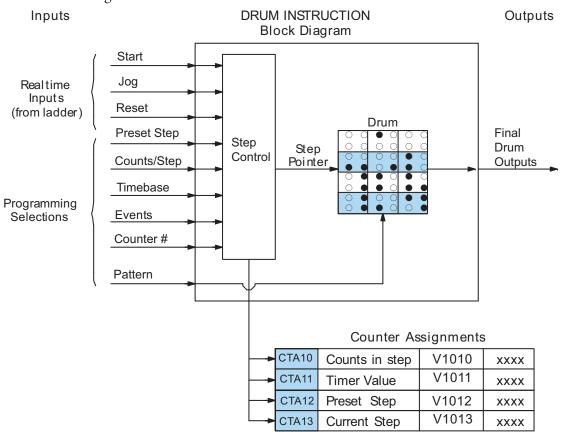

| Counter Assignments                        |

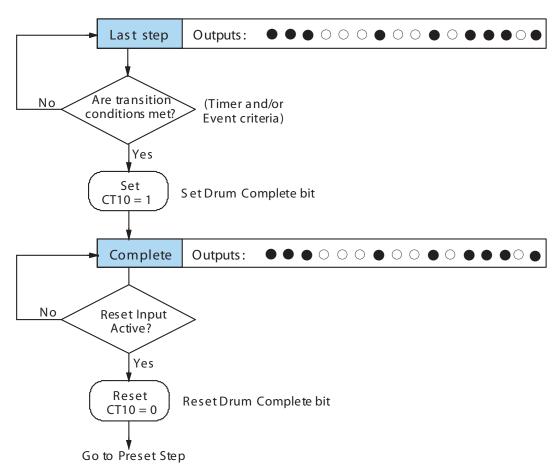

| Last Step Completion                       |

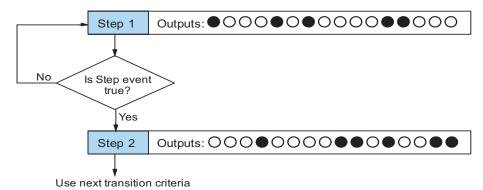

| Overview of Drum Operation6-               |

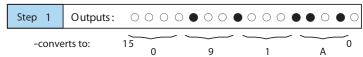

| Drum Instruction Block Diagram6-           |

| Powerup State of Drum Registers6-          |

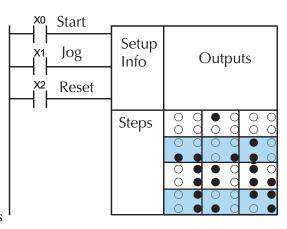

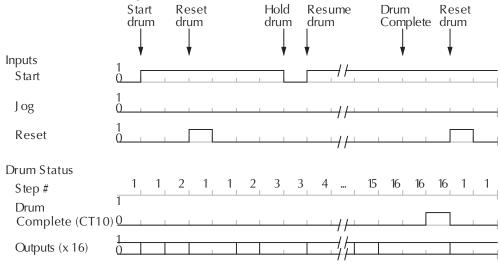

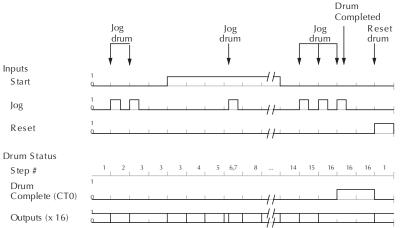

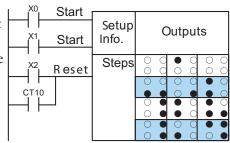

| Drum Control Techniques6-1                 |

| Drum Control Inputs6–1                     |

| Self-Resetting Drum                        |

| Initializing Drum Outputs                  |

| Using Complex Event Step Transitions6–1    |

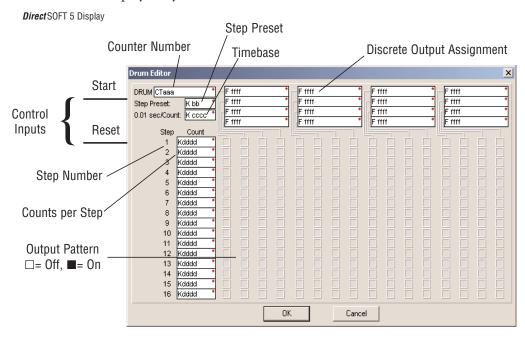

| Drum Instruction                           |

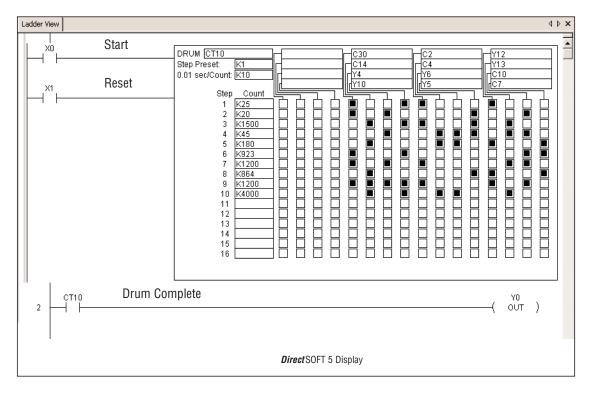

| Timed Drum with Discrete Outputs (DRUM)6–1 |

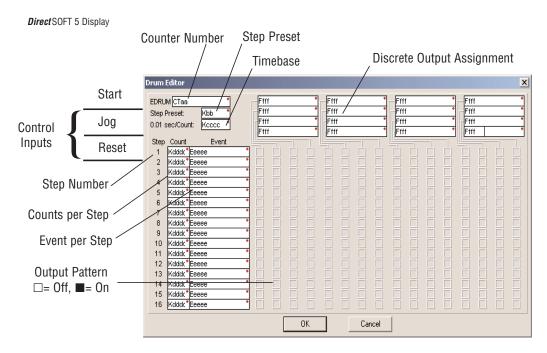

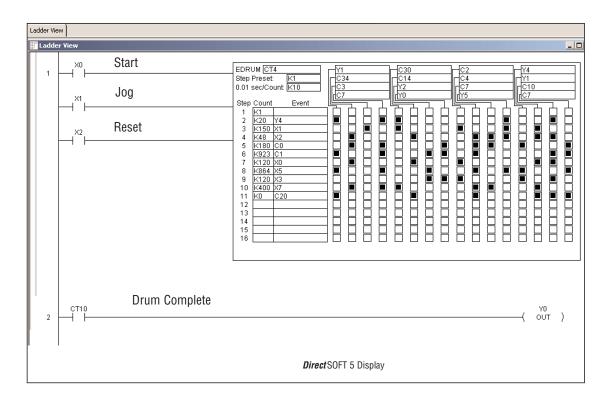

| Event Drum (EDRUM)                         |

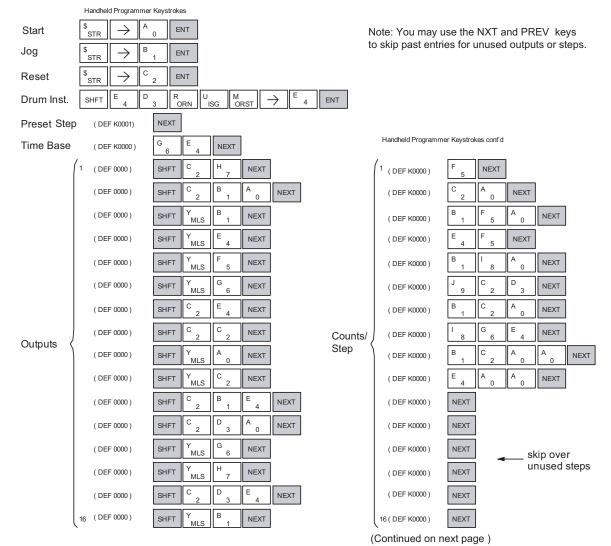

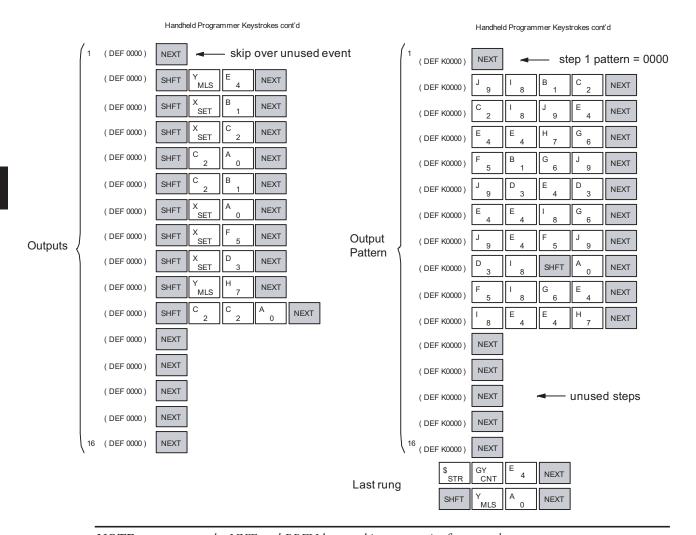

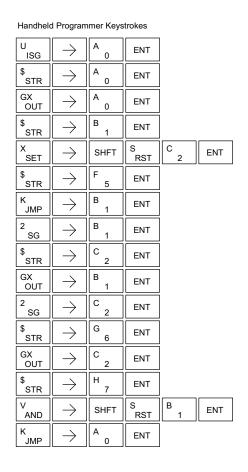

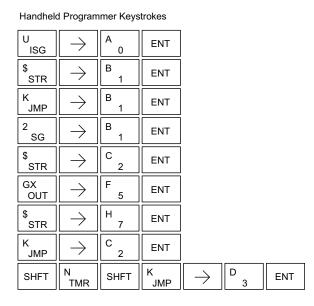

| Handheld Programmer Drum Mnemonics6–1      |

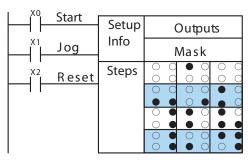

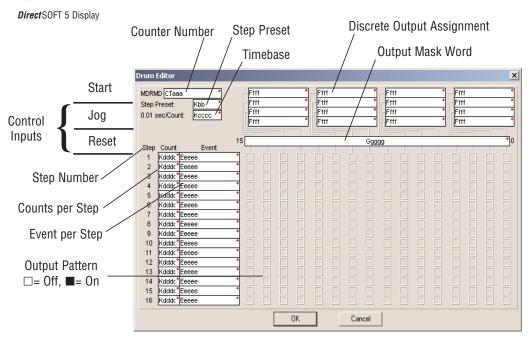

| Masked Event Drum with Discrete Outputs (MDRMD)                                             |     |

|---------------------------------------------------------------------------------------------|-----|

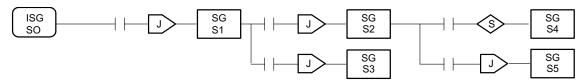

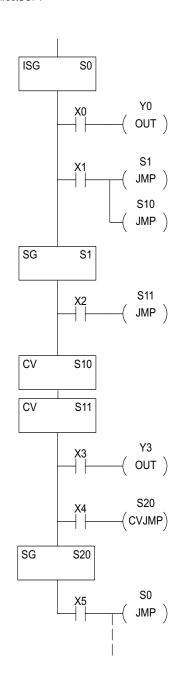

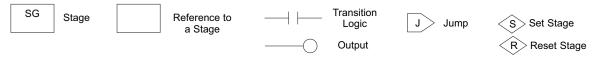

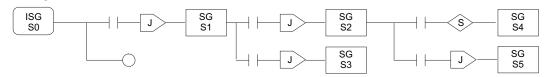

| Chapter 7: RLL <sup>PLUS</sup> Stage Programming                                            |     |

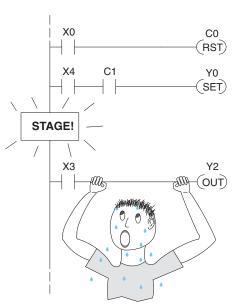

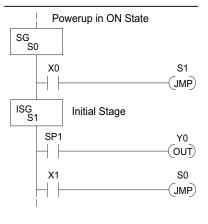

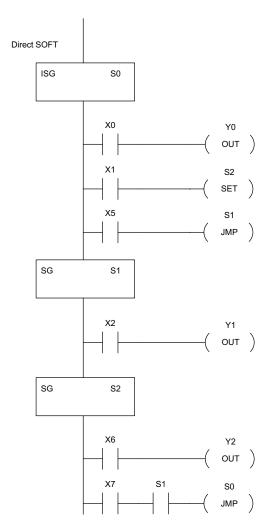

| Introduction to Stage Programming                                                           |     |

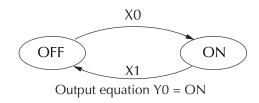

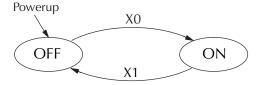

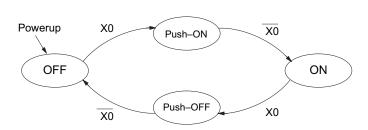

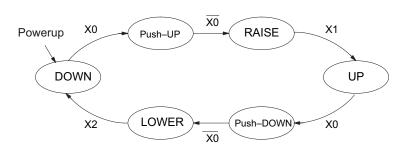

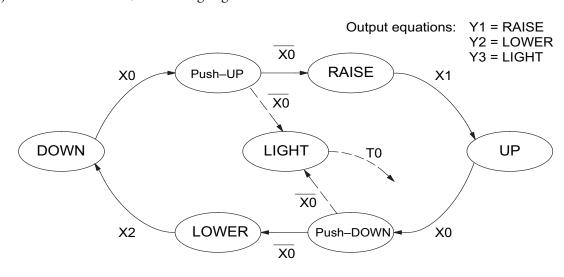

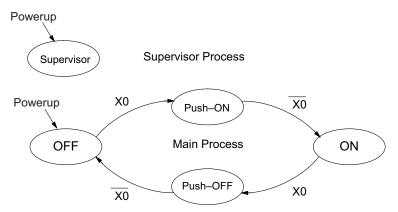

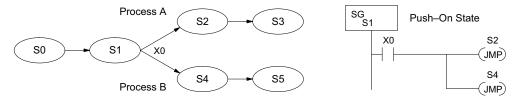

| Learning to Draw State Transition Diagrams                                                  |     |

| The Need for State Diagrams                                                                 |     |

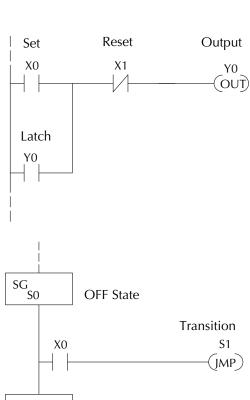

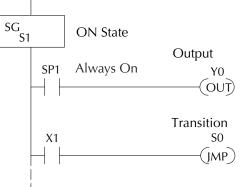

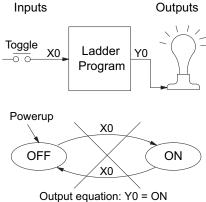

| A 2-State Process                                                                           |     |

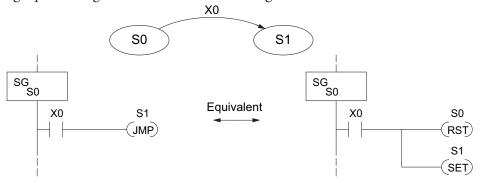

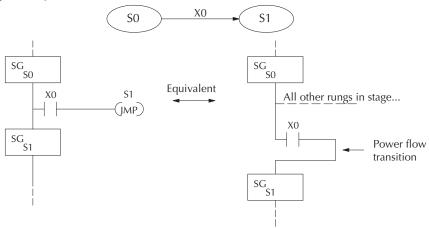

| Stage Equivalent                                                                            |     |

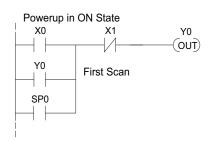

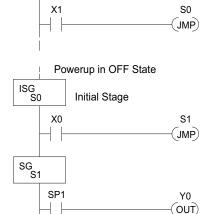

| Initial Stages                                                                              |     |

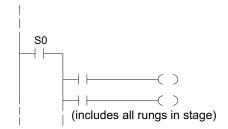

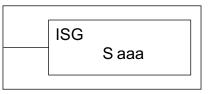

| Stage Instruction Characteristics                                                           |     |

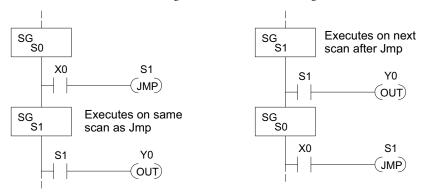

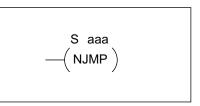

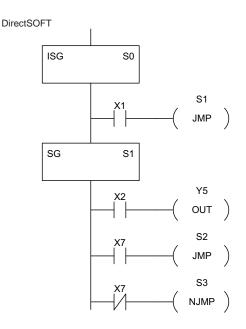

| Using the Stage Jump Instruction for State Transitions                                      |     |

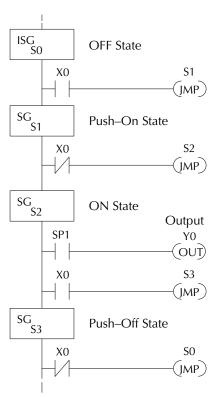

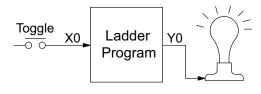

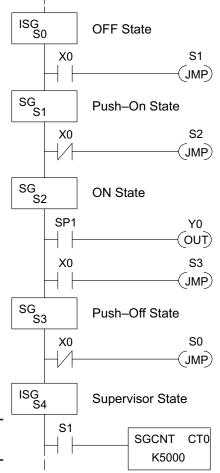

| Stage Program Example: Toggle On/Off Lamp Controller                                        |     |

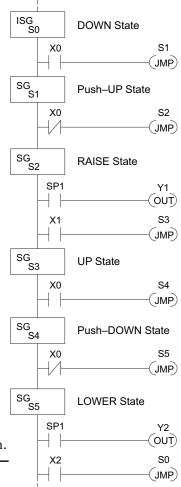

| Four Steps to Writing a Stage Program                                                       |     |

| 2. Draw the Block Diagram                                                                   | 7–9 |

| <ul><li>3. Draw the State Transition Diagram.</li><li>4. Write the Stage Program.</li></ul> |     |

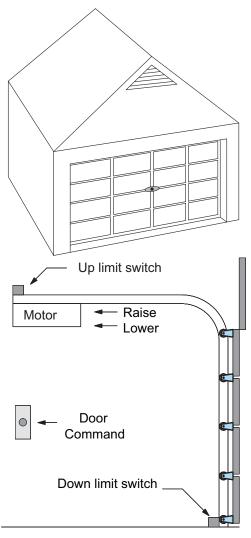

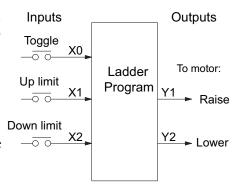

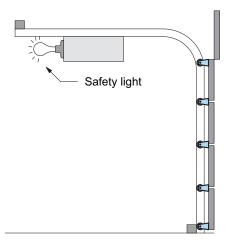

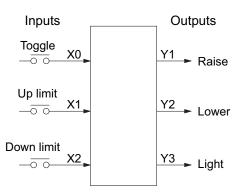

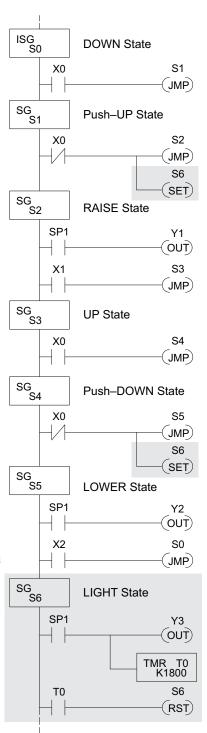

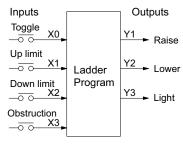

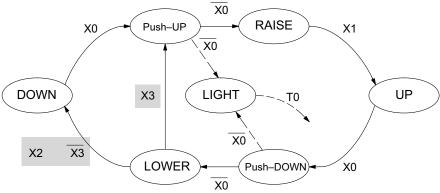

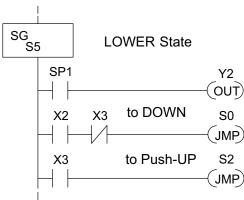

| Stage Program Example: A Garage Door Opener                                                 |     |

| Draw the Block Diagram                                                                      |     |

| Add Safety Light Feature                                                                    |     |

| Using a Timer Inside a Stage                                                                |     |

| Add Emergency Stop Feature                                                                  |     |

| Stage Program Design Considerations                                                         |     |

| Stage Program Organization  How Instructions Work Inside Stages  Using a Stage as a Supervisory Process  Stage Counter  Power Flow Transition Technique |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Stage View in DirectSOFT 5                                                                                                                              |     |

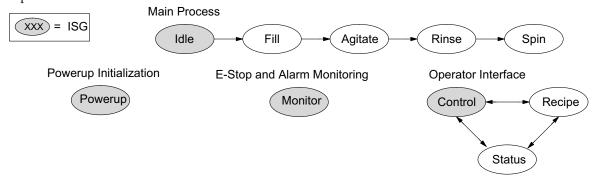

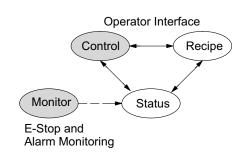

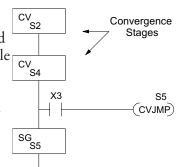

| Parallel Processes                                                                                                                                      |     |

| Converging Processes                                                                                                                                    |     |

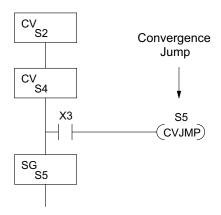

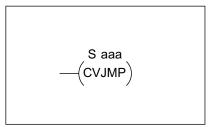

| Convergence Stages (CV)                                                                                                                                 |     |

| Convergence Jump (CVJMP)                                                                                                                                |     |

| Convergence Stage Guidelines                                                                                                                            |     |

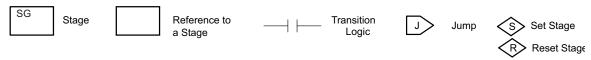

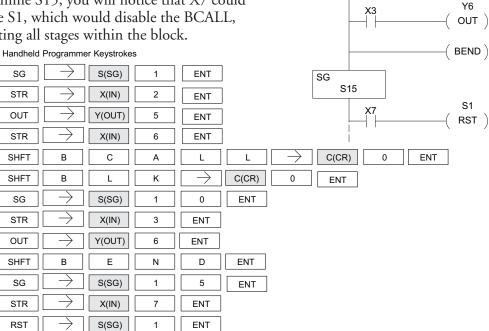

| RLLPLUS (Stage) Instructions                                                                                                                            |     |

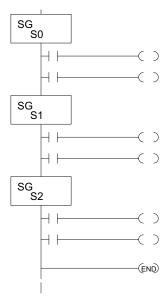

| Stage (SG)                                                                                                                                              |     |

| Initial Stage (ISG)                                                                                                                                     |     |

| Jump (JMP)                                                                                                                                              |     |

| Converge Stage (CV) and Converge Jump (CVJMP)                                                                                                           |     |

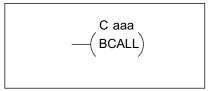

| Block Call (BCALL)                                                                                                                                      |     |

| Block (BLK)                                                                                                                                             |     |

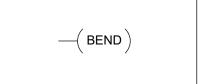

| Block End (BEND)                                                                                                                                        |     |

| Questions and Answers about Stage Programming                                                                                                           |     |

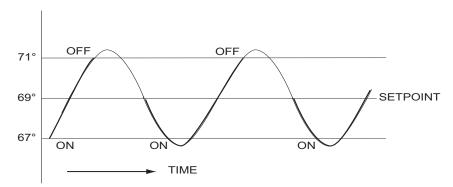

| Chapter 8: PID Loop Operation                                                                                                                           |     |

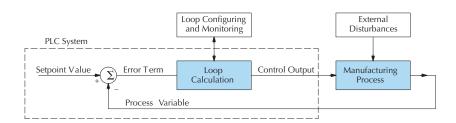

| DL06 PID Control                                                                                                                                        | 8_2 |

| DL06 PID Control Features                                                                                                                               |     |

| Introduction to PID Control                                                                                                                             |     |

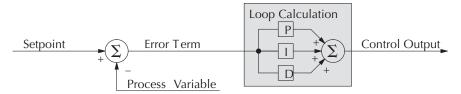

| What is PID Control?                                                                                                                                    | 8–4 |

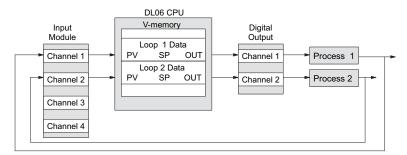

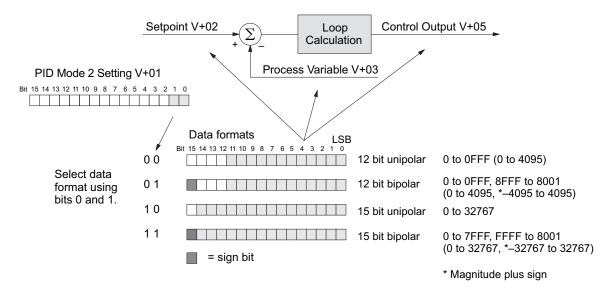

| Introducing DL06 PID Control                                                                                                                            | 8–6 |

| Process Control Definitions                                                                                                                             | 8–8 |

| PID Loop Operation                                                                                                                                      | 8–9 |

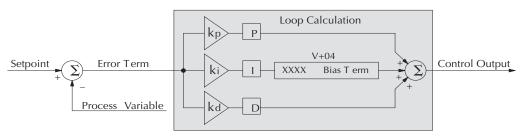

| Position Form of the PID Equation                                                                                                                       | 8–9 |

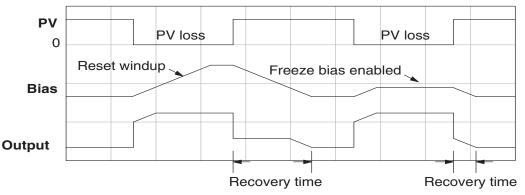

| Reset Windup Protection                                                                                                                                 |     |

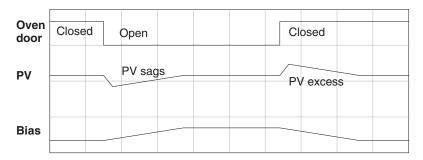

| Freeze Bias                                                                                                                                             |     |

| Adjusting the Bias                                                                                                                                      |     |

| Step Bias Proportional to Step Change in SP             | 8–12 |

|---------------------------------------------------------|------|

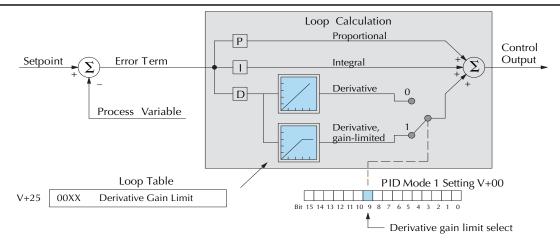

| Eliminating Proportional, Integral or Derivative Action | 8–12 |

| Velocity Form of the PID Equation                       | 8–12 |

| Bumpless Transfer                                       | 8–13 |

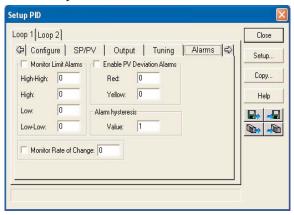

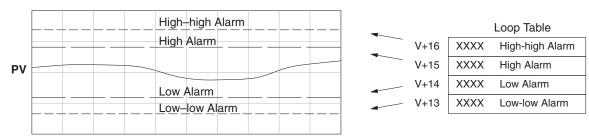

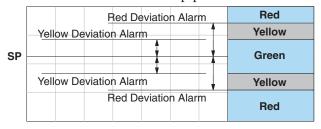

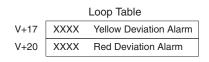

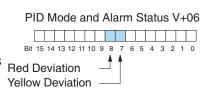

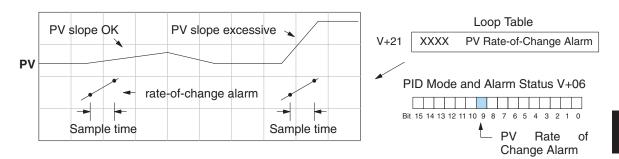

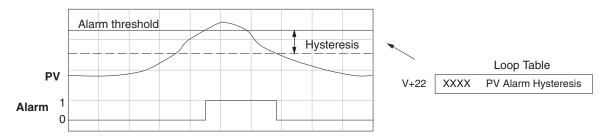

| Loop Alarms                                             | 8–13 |

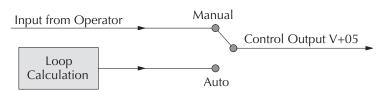

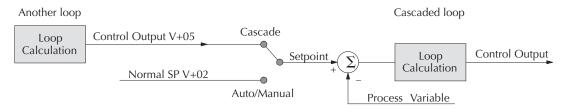

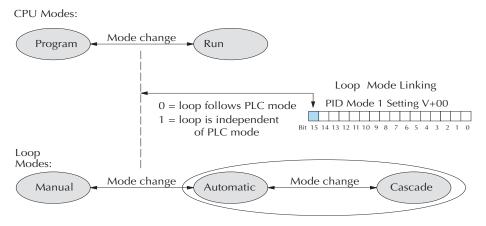

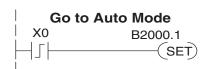

| Loop Operating Modes                                    | 8–14 |

| Special Loop Calculations                               | 8–14 |

| Ten Steps to Successful Process Control                 | 8–16 |

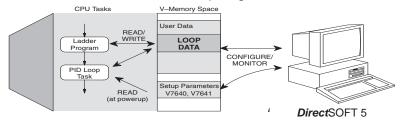

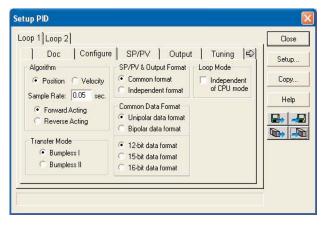

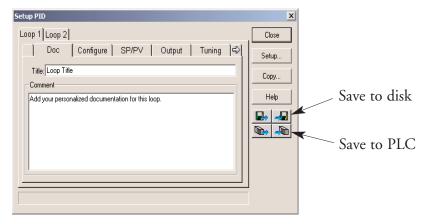

| PID Loop Setup                                          | 8–18 |

| Some Things to Do and Know Before Starting              | 8–18 |

| PID Error Flags                                         | 8–18 |

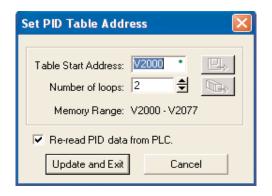

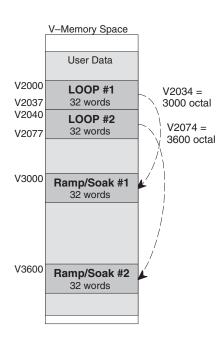

| Establishing the Loop Table Size and Location           | 8–18 |

| Loop Table Word Definitions                             | 8–20 |

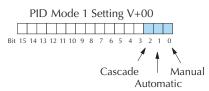

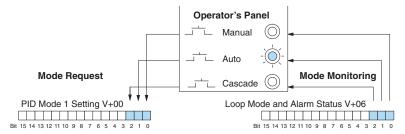

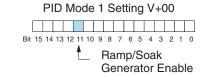

| PID Mode Setting 1 Bit Descriptions (Addr + 00)         | 8–21 |

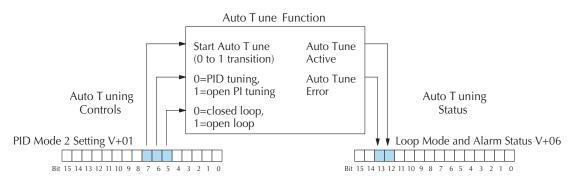

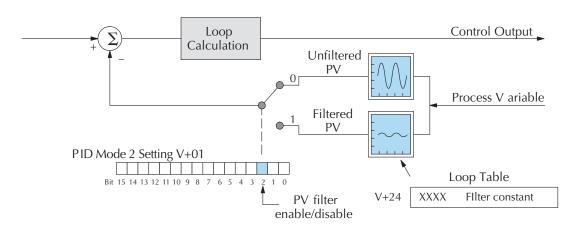

| PID Mode Setting 2 Bit Descriptions (Addr + 01)         | 8–22 |

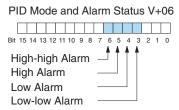

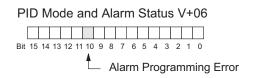

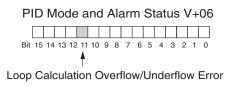

| Mode/Alarm Monitoring Word (Addr + 06)                  | 8–23 |

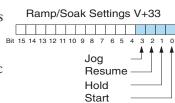

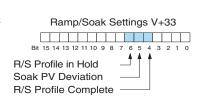

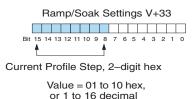

| Ramp/Soak Table Flags (Addr + 33)                       | 8–23 |

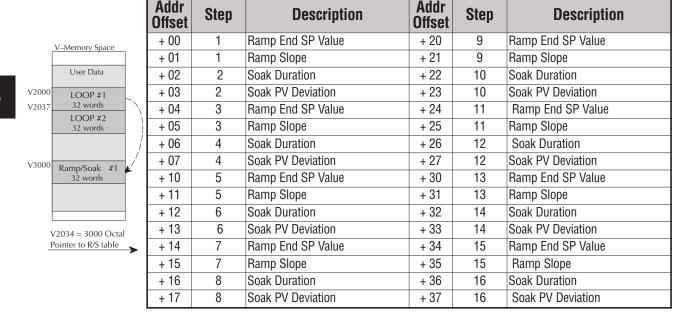

| Ramp/Soak Table Location (Addr + 34)                    | 8–24 |

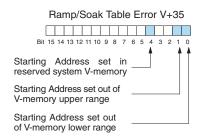

| Ramp/Soak Table Programming Error Flags (Addr + 35)     | 8–24 |

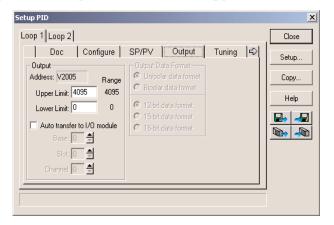

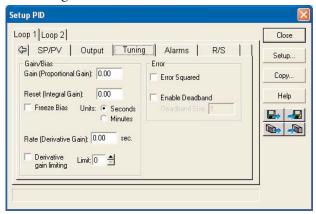

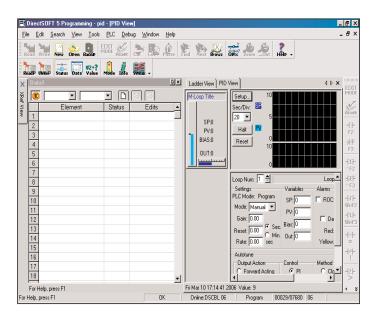

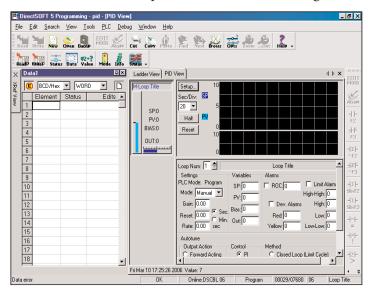

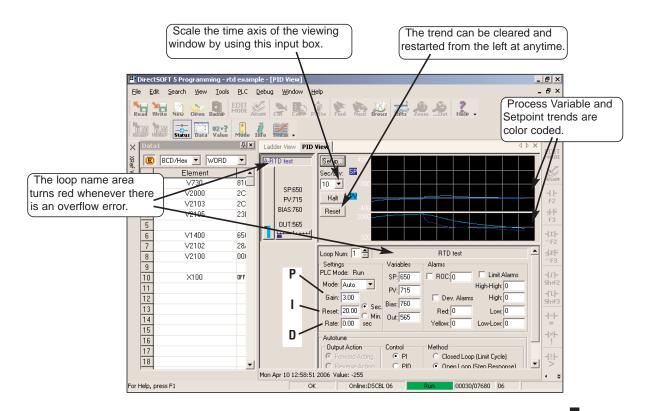

| Configure the PID Loop                                  | 8–25 |

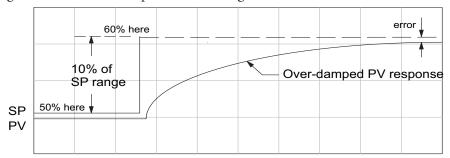

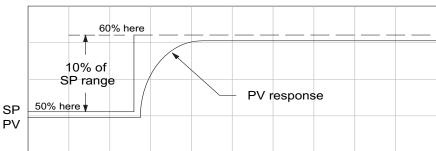

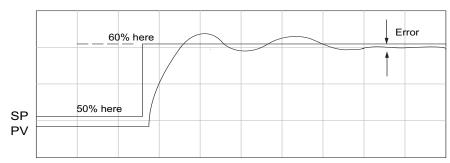

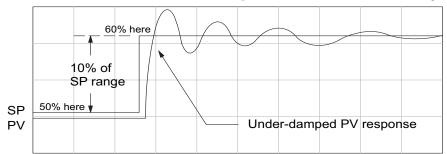

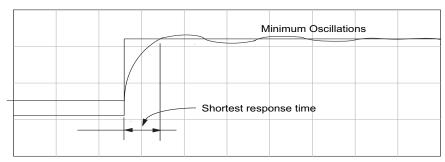

| PID Loop Tuning                                         | 8–40 |

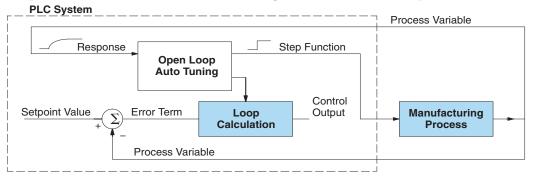

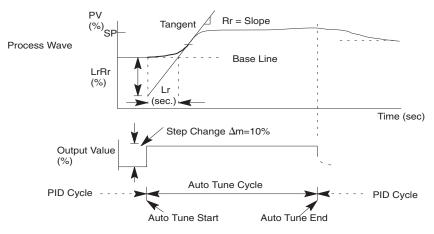

| Open-Loop Test                                          |      |

| Manual Tuning Procedure                                 |      |

| Alternative Manual Tuning Procedures by Others          |      |

| Tuning PID Controllers                                  |      |

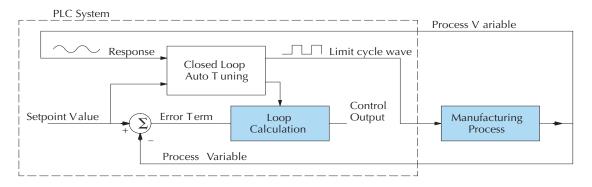

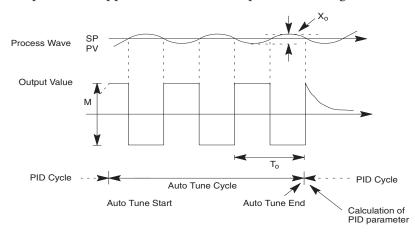

| Auto Tuning Procedure                                   |      |

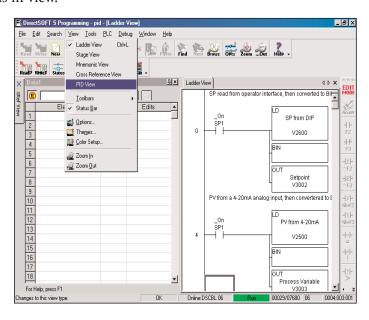

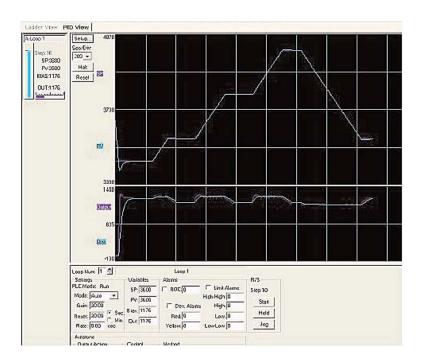

| Use DirectSOFT 5 Data View with PID View                | 8–49 |

| Open a New Data View Window                             | 8–49 |

| Open PID View                                           |      |

| Using the Special PID Features                          | 8–53 |

| How to Change Loop Modes                                | 8–53 |

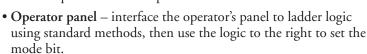

| Operator Panel Control of PID Modes                     | 8–54 |

| PLC Modes Effect on Loop Modes                          |      |

| Loop Mode Override                                      |      |

| PV Analog Filter                                        |      |

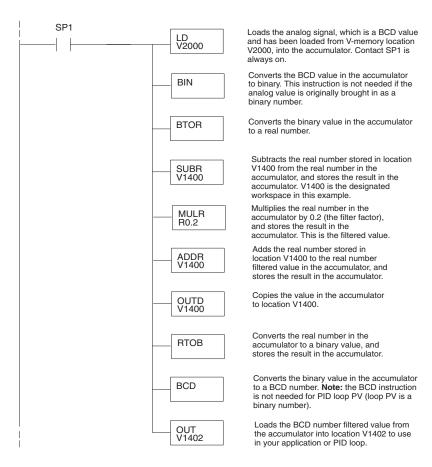

| Creating an Analog Filter in Ladder Logic               |      |

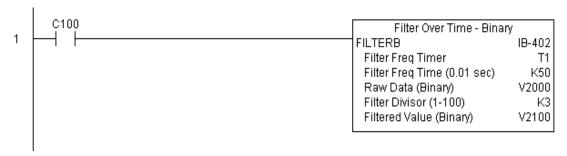

| Use the <i>Direct</i> SOFT 5 Filter Intelligent Box Instructions FilterB Example |      |

|----------------------------------------------------------------------------------|------|

| •                                                                                |      |

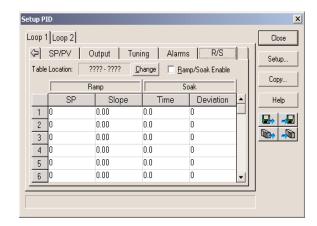

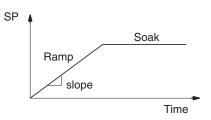

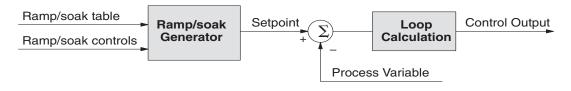

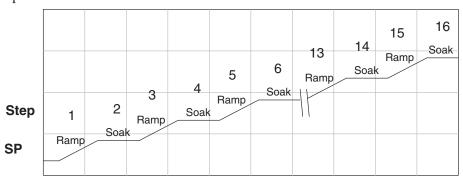

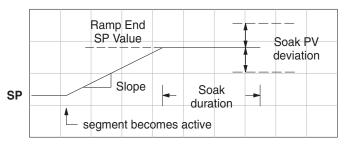

| Ramp/Soak Generator                                                              |      |

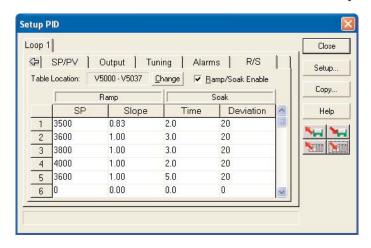

| Ramp/Soak Table                                                                  |      |

| Ramp/Soak Table Flags                                                            |      |

| Ramp/Soak Generator Enable                                                       |      |

| Ramp/Soak Controls                                                               |      |

| Ramp/Soak Profile Monitoring                                                     |      |

| Ramp/Soak Programming Errors                                                     |      |

| Testing Your Ramp/Soak Profile                                                   | 8–62 |

| DirectSOFT 5 Ramp/Soak Example                                                   | 8-63 |

| Setup the Profile in PID Setup                                                   | 8-63 |

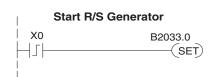

| Program the Ramp/Soak Control in Relay Ladder                                    | 8-63 |

| Test the Profile                                                                 | 8-64 |

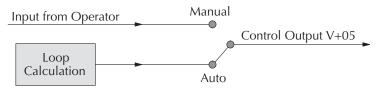

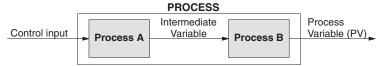

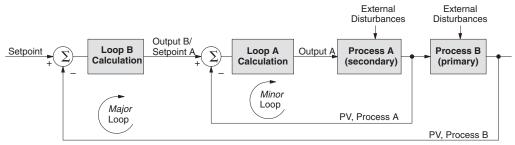

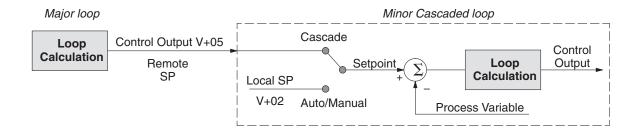

| Cascade Control                                                                  | 8–65 |

| Introduction                                                                     | 8–65 |

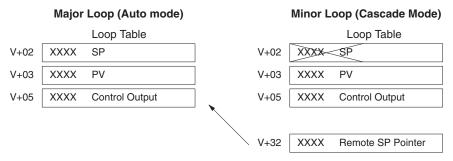

| Cascaded Loops in the DL06 CPU                                                   |      |

| Tuning Cascaded Loops                                                            | 8–67 |

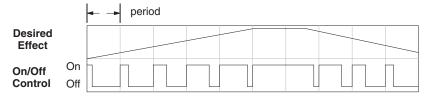

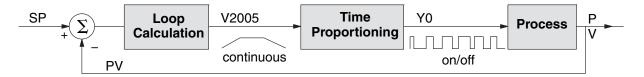

| Time-Proportioning Control                                                       |      |

| On/Off Control Program Example                                                   | 8–69 |

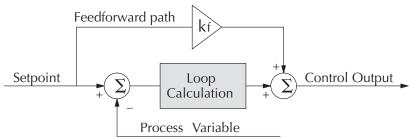

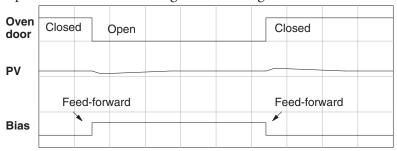

| Feedforward Control                                                              | 8–70 |

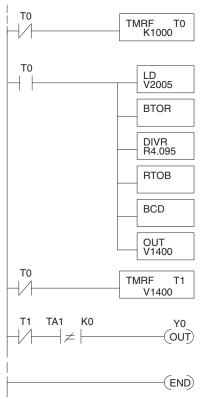

| Feedforward Example                                                              | 8–71 |

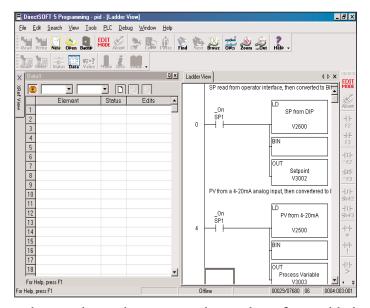

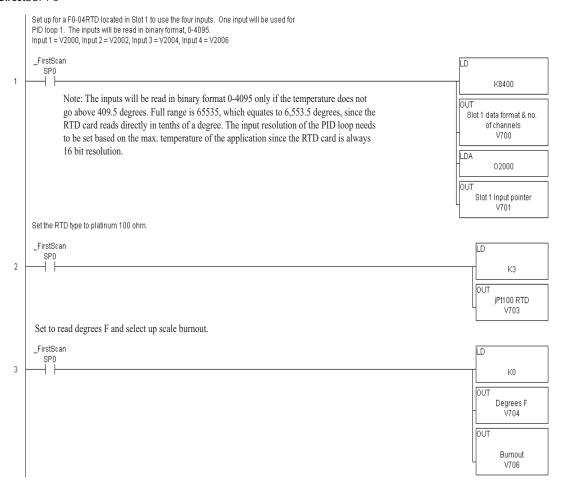

| PID Example Program                                                              | 8–72 |

| Program Setup for the PID Loop                                                   | 8–72 |

| Troubleshooting Tips                                                             | 8–75 |

| Glossary of PID Loop Terminology                                                 | 8–77 |

| Bibliography                                                                     | 8–79 |

|                                                                                  |      |

| Chapter 9: Maintenance and Troubleshooting                                       |      |

| Hardware System Maintenance                                                      | 9–2  |

| Standard Maintenance                                                             | 9–2  |

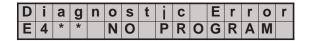

| Diagnostics                                                                      | 9–2  |

| Diagnostics                                                                      | 9–2  |

|   | Fatal Errors                                                | .9–2  |

|---|-------------------------------------------------------------|-------|

|   | Non-fatal Errors                                            | .9–2  |

|   | V-memory Error Code Locations                               |       |

|   | Special Relays (SP) Corresponding to Error Codes            |       |

|   | DL06 Micro PLC Error Codes                                  |       |

|   | Program Error Codes                                         | .9–5  |

|   | CPU Indicators                                              | .9–6  |

|   | PWR Indicator                                               | .9–6  |

|   | RUN Indicator                                               | .9–7  |

|   | CPU Indicator                                               | .9–7  |

|   | Communications Problems                                     | .9–7  |

|   | I/O Point Troubleshooting                                   | .9–8  |

|   | Possible Causes                                             |       |

|   | Some Quick Steps                                            | .9–8  |

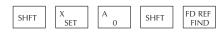

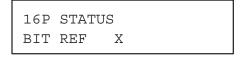

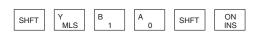

|   | Handheld Programmer Keystrokes Used to Test an Output Point | .9–9  |

|   | Noise Troubleshooting                                       | 9–10  |

|   | Electrical Noise Problems                                   | 9–10  |

|   | Reducing Electrical Noise                                   | 9–10  |

|   | Machine Startup and Program Troubleshooting                 | 9–11  |

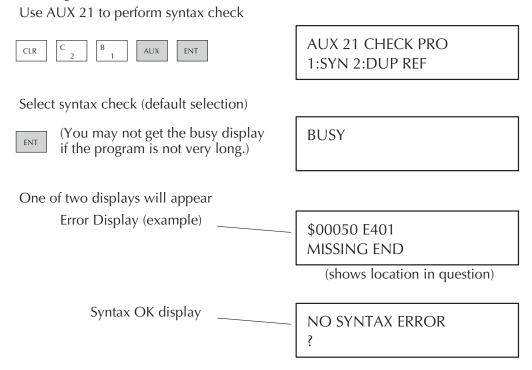

|   | Syntax Check                                                | 9–11  |

|   | Special Instructions                                        |       |

|   | Duplicate Reference Check                                   |       |

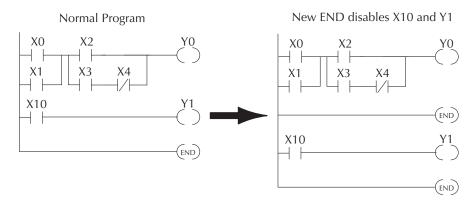

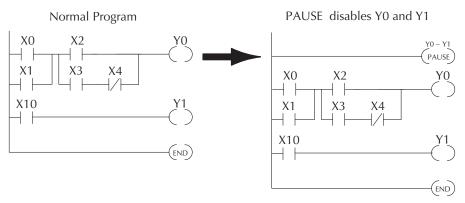

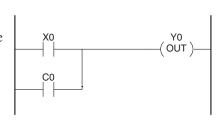

|   | Run Time Edits                                              |       |

|   | Run Time Edit Example                                       |       |

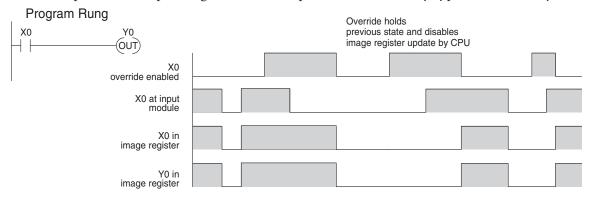

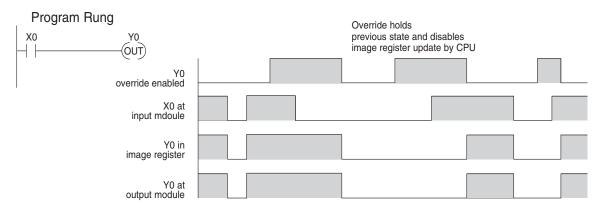

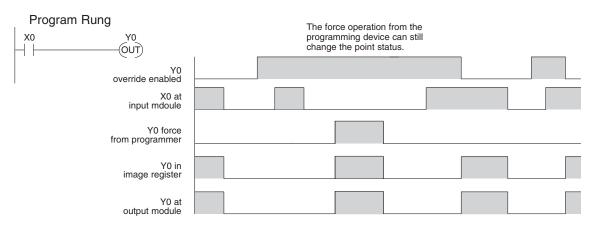

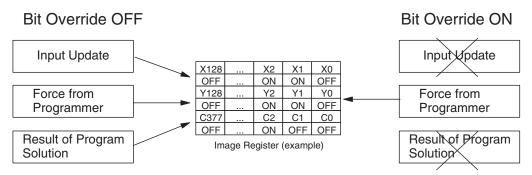

|   | Forcing I/O Points                                          |       |

|   | Regular Forcing with Direct Access                          |       |

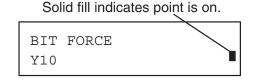

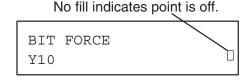

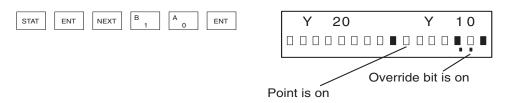

|   | Bit Override Forcing                                        |       |

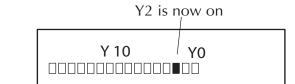

|   | Bit Override Indicators                                     | 9–19  |

| C | Chapter 10: LCD Display Panel                               |       |

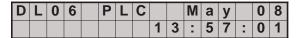

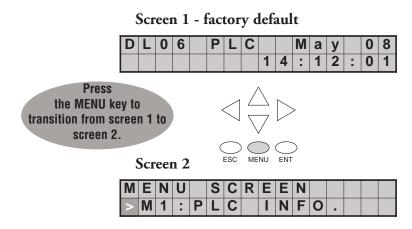

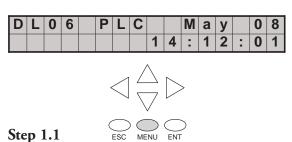

|   | Introduction to the DL06 LCD Display Panel                  | 10–2  |

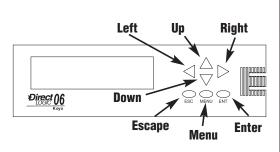

|   | Keypad                                                      |       |

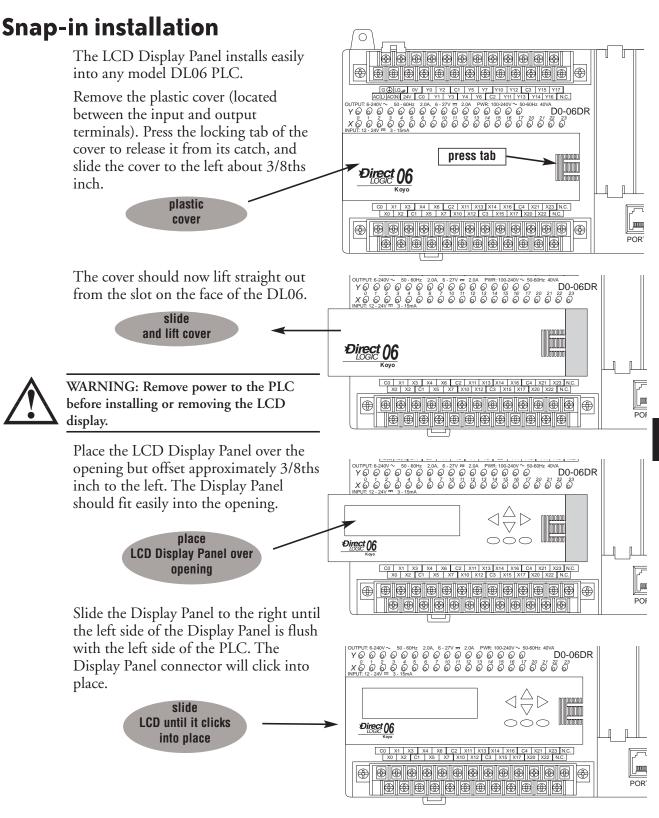

|   | Snap-in installation                                        |       |

|   | Display Priority                                            |       |

|   |                                                             | 1 U T |

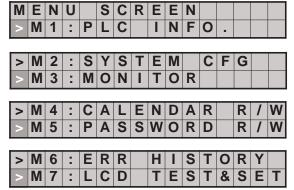

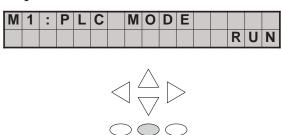

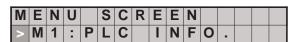

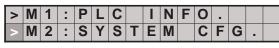

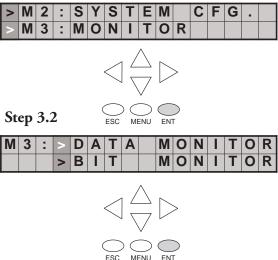

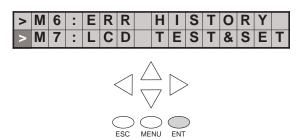

| N  | /lenu Navigation                                                                            |

|----|---------------------------------------------------------------------------------------------|

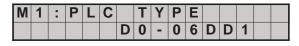

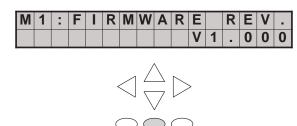

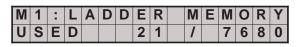

| C  | Confirm PLC Type, Firmware Revision Level, Memory Usage, Etc. $\dots \dots 10$ – $\epsilon$ |

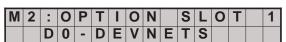

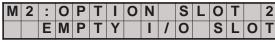

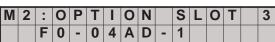

| E  | xamining Option Slot Contents10–8Menu 2, M2:SYSTEM CFG                                      |

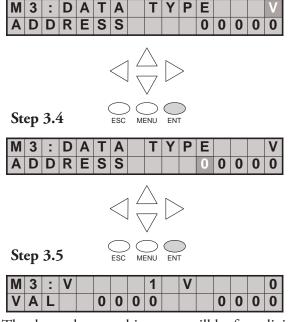

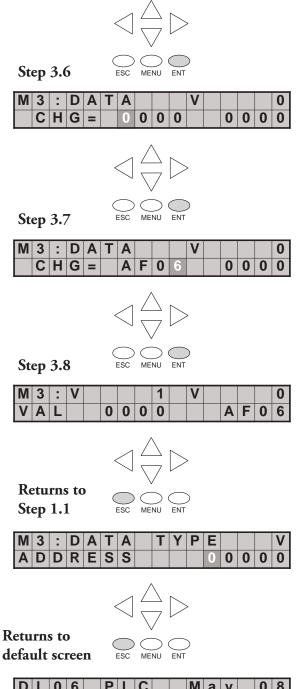

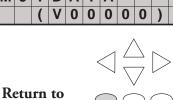

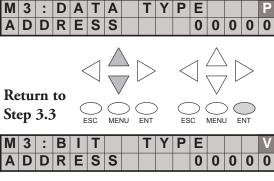

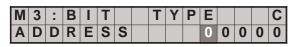

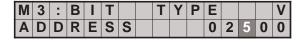

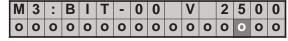

| N  | Monitoring and Changing Data Values                                                         |

| В  | Bit Monitor                                                                                 |

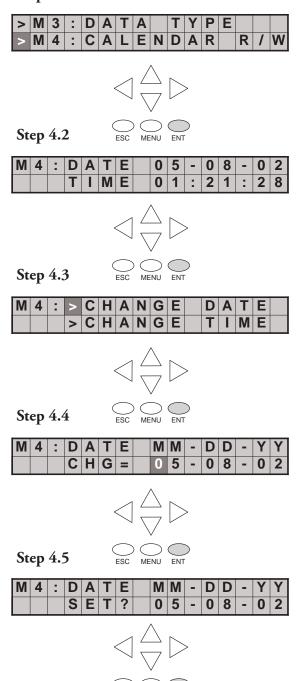

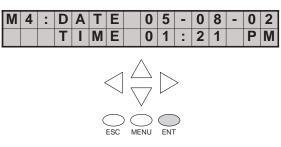

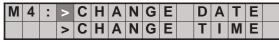

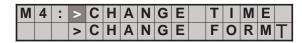

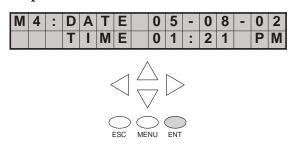

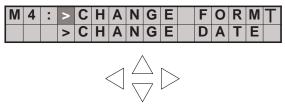

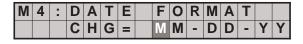

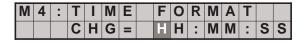

| C  | Changing Date and Time                                                                      |

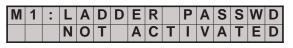

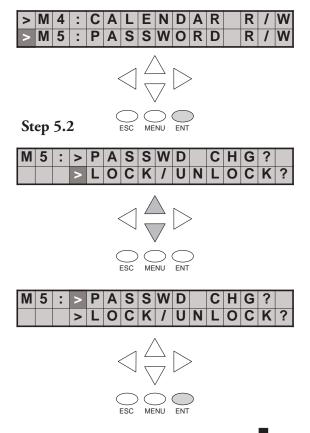

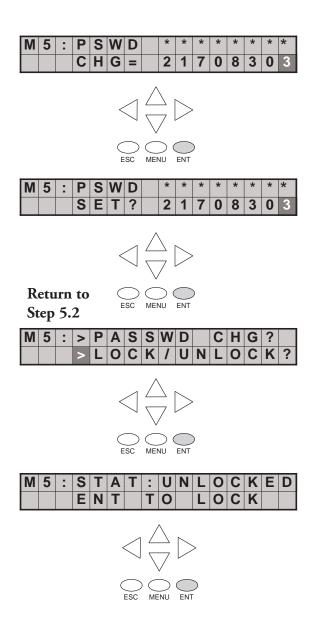

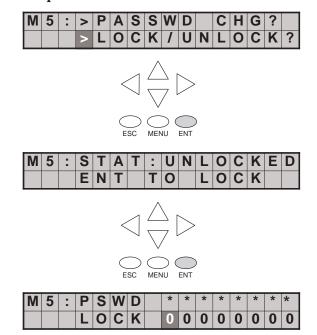

| S  | etting Password and Locking                                                                 |

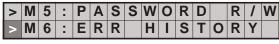

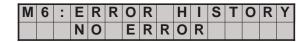

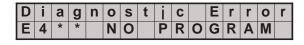

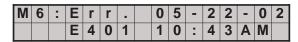

| R  | Menu 6, M6 : ERR HISTORY                                                                    |

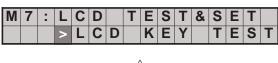

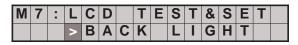

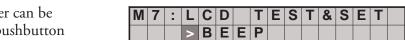

| T  | Oggle Light and Beeper, Test Keys                                                           |

| P  | CLC Memory Information for the LCD Display Panel                                            |

| C  | Changing the Default Screen                                                                 |

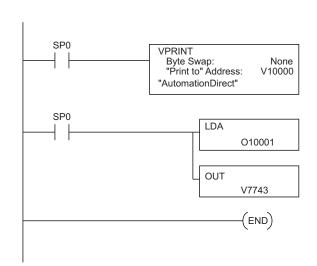

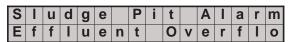

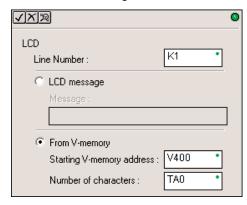

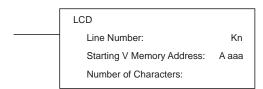

| C  | Source of message                                                                           |

| Αp | pendix A: Auxiliary Functions                                                               |

| 1. | $\Delta_{-2}$                                                                               |

| Purpose of Auxiliary Functions                      |     |

|-----------------------------------------------------|-----|

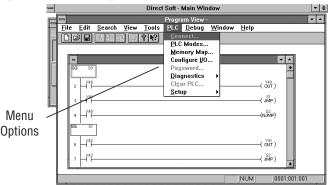

| Accessing AUX Functions via DirectSOFT 5            |     |

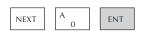

| Accessing AUX Functions via the Handheld Programmer |     |

| AUX 2* — RLL Operations                             |     |

| AUX 21 Check Program                                |     |

| AUX 22 Change Reference                             |     |

| AUX 23 Clear Ladder Range                           |     |

| AUX 24 Clear Ladders                                |     |

| AUX 3* — V-memory Operations                        | A–4 |

| AUX 31 Clear V-memory                               |     |

| <b>AUX 4*</b> — I/O Configuration                   |     |

| AUX 41 Show I/O Configuration                       |     |

| AUX 5* — CPU Configuration                          | A–5 |

| AUX 51 Modify Program Name                          |     |

| AUX 53 Display Scan Time                            |     |

| AUX 54 Initialize Scratchpad                        |     |

| AUX 55 Set Watchdog Timer                           |     |

| AUX 56 CPU Network Address                          | A-6 |

| AUX 57 Set Retentive Ranges                         |     |

| AUX 58 Test Operations                              |     |

| AUX 59 Bit Override                                 |     |

| AUX 5B Counter Interface Configuration              |     |

| AUX 5D Select PLC Scan Mode                         |     |

| AUX 6* — Handheld Programmer Configuration          |     |

| AUX 61 Show Revision Numbers                        |     |

| AUX 62 Beeper On/Off                                |     |

| AUX 65 Run Self Diagnostics                         |     |

| AUX 7* — EEPROM Operations                          |     |

| Transferrable Memory Areas                          |     |

| AUX 71 CPU to HPP EEPROM                            |     |

| AUX 72 HPP EEPROM to CPU                            |     |

| AUX 73 Compare HPP EEPROM to CPU                    |     |

| AUX 74 HPP EEPROM Blank Check                       |     |

| AUX 75 Erase HPP EEPROM                             |     |

| AUX 76 Show EEPROM Type                             | A–9 |

| AUX 8* — Password Operations            | _9<br>10 |

|-----------------------------------------|----------|

| Appenedix B: DL06 Error codes           |          |

| DL06 Error Codes                        | -2       |

| Appendix C: Instruction Execution Times |          |

| Introduction                            | _2       |

| V-Memory Data Registers                 |          |

| V-Memory Bit Registers                  |          |

| How to Read the Tables                  |          |

| Instruction Execution Times             | _3       |

| Boolean Instructions                    |          |

| Comparative Boolean Instructions        |          |

| Immediate Instructions                  |          |

| Bit of Word Boolean Instructions        |          |

| Timer, Counter and Shift Register       |          |

| Accumulator Data Instructions           |          |

| Logical Instructions                    |          |

| Math Instructions                       |          |

| Differential Instructions               | 19       |

| Bit Instructions                        | 19       |

| Number Conversion Instructions          | 20       |

| Table Instructions                      | 20       |

| CPU Control Instructions                | 22       |

| Program Control Instructions            |          |

| Interrupt Instructions                  | 22       |

| Network Instructions                    |          |

| Intelligent I/O Instructions            |          |

| Message Instructions                    |          |

| RLLplus Instructions                    |          |

| Drum Instructions                       |          |

| Clock / Calender Instructions           |          |

| MODBUS Instructions                     | 24       |

| ASCII Instructions                                     | C–24         |

|--------------------------------------------------------|--------------|

| Appendix D: Special Relays                             |              |

|                                                        | D 2          |

| DL06 PLC Special Relays                                |              |

| Startup and Real-Time Relays                           |              |

| CPU Status Relays                                      |              |

| Accumulator Status                                     |              |

| HSIO Input Status                                      |              |

| HSIO Pulse Output Relay                                |              |

| Communication Monitoring Relay                         |              |

| Option Slot Communication Monitoring Relay             |              |

| Option Slot Special Relay                              |              |

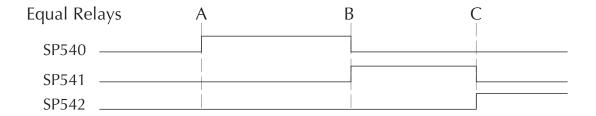

| Counter 1 Mode 10 Equal Relays                         |              |

| Counter 2 Mode 10 Equal Relays                         |              |

| 4                                                      |              |

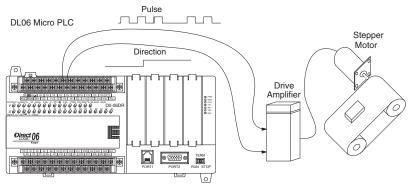

| Appendix E: High-speed Input and Pulse Output Features |              |

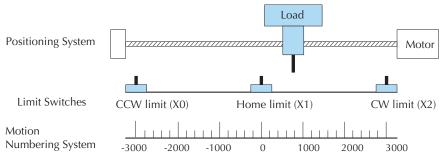

| Introduction                                           | E–2          |

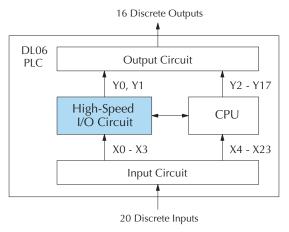

| Built-in Motion Control Solution                       | E–2          |

| Availability of HSIO Features                          | E–2          |

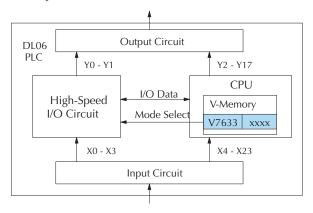

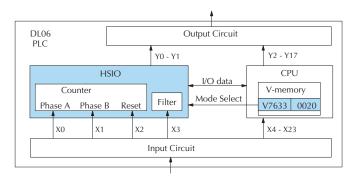

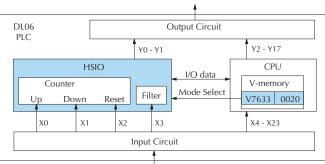

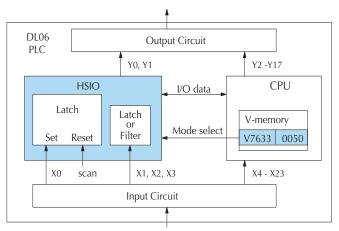

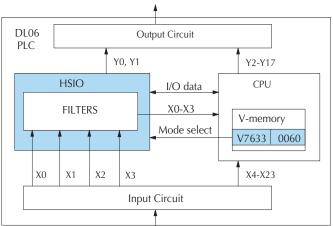

| Dedicated High- Speed I/O Circuit                      | E-3          |

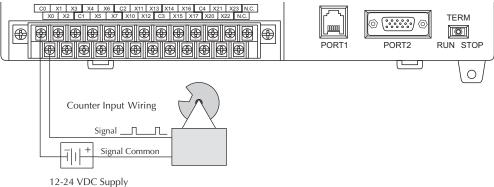

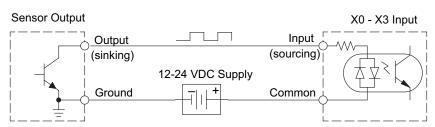

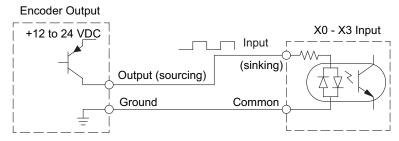

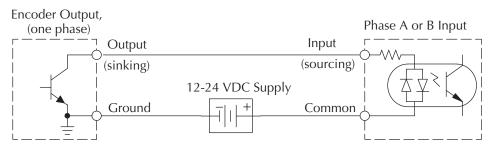

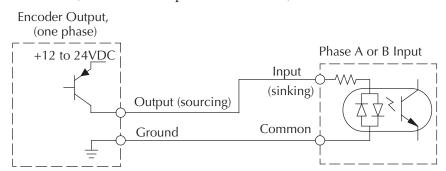

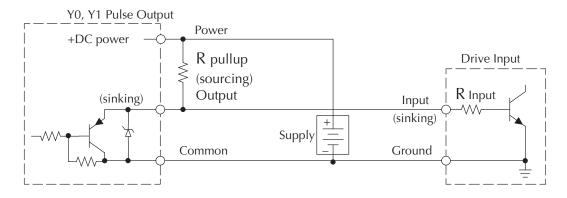

| Wiring Diagrams for Each HSIO Mode                     | E-3          |

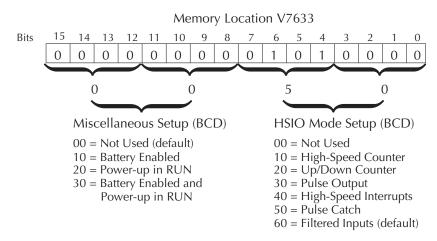

| Choosing the HSIO Operating Mode                       | <b>.</b> E–4 |

| Understanding the Six Modes                            |              |

| Default Mode                                           |              |

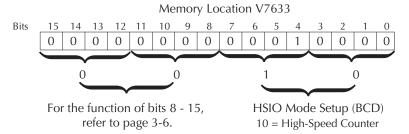

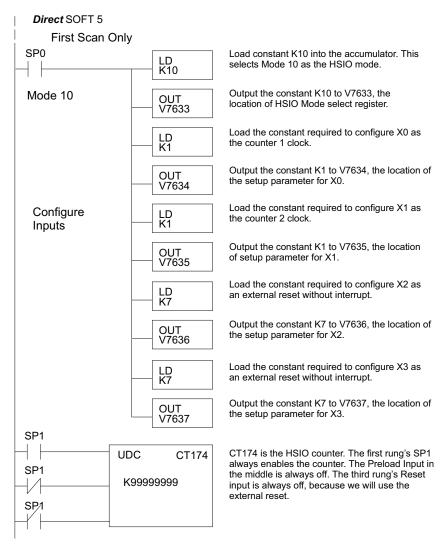

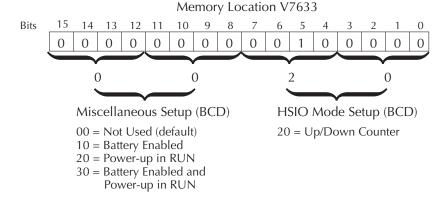

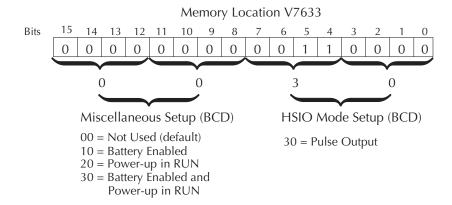

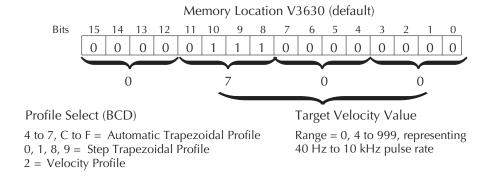

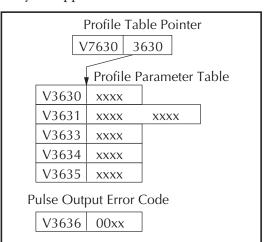

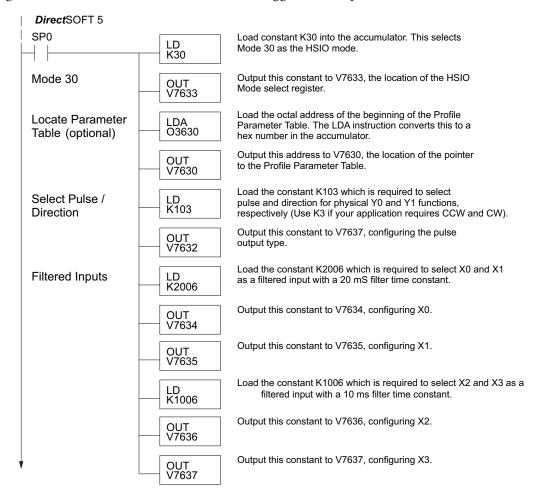

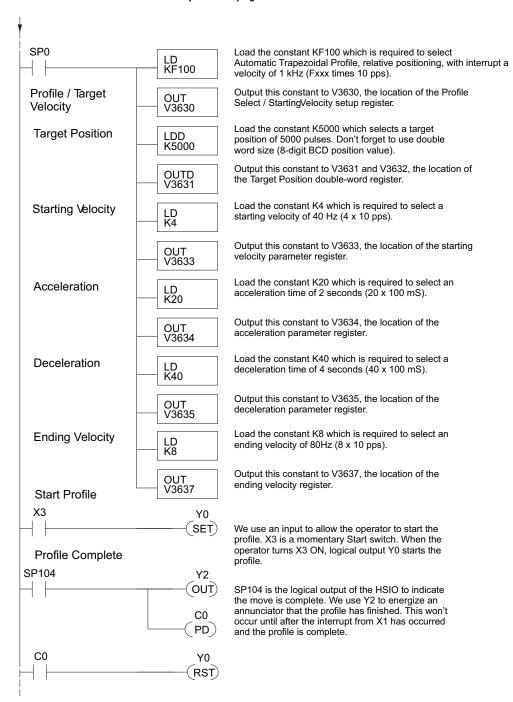

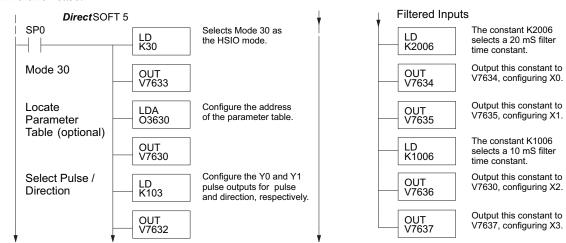

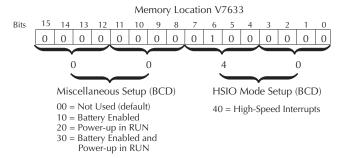

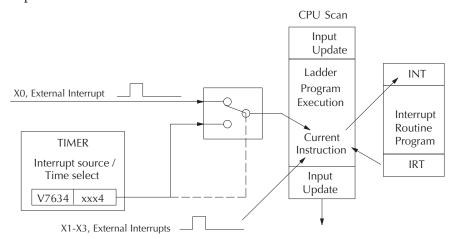

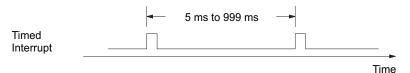

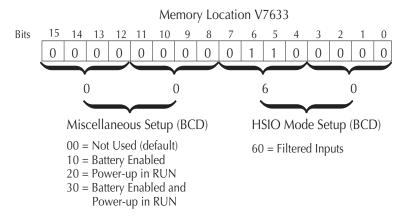

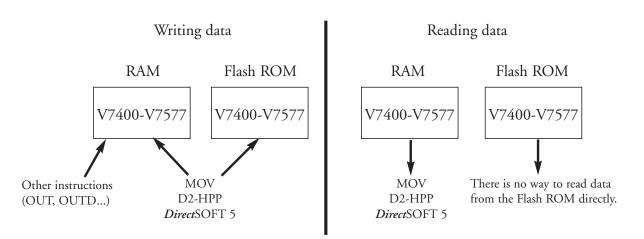

| Configuring the HSIO Mode                              |              |

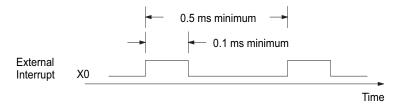

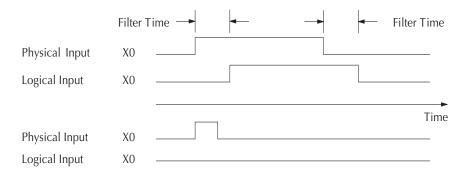

| Configuring Inputs X0 – X3                             |              |

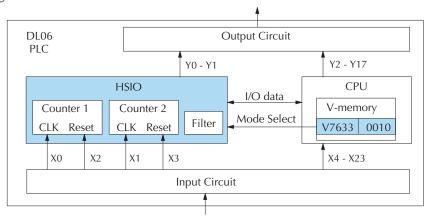

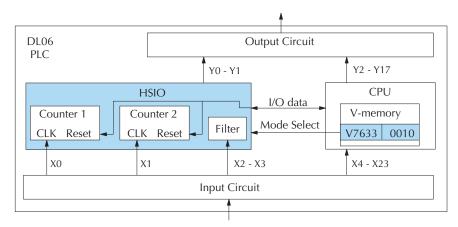

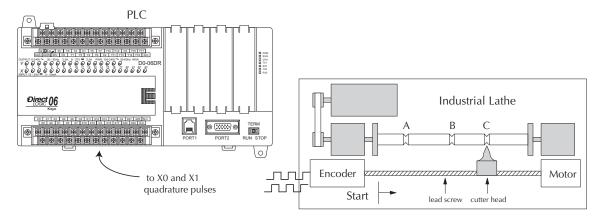

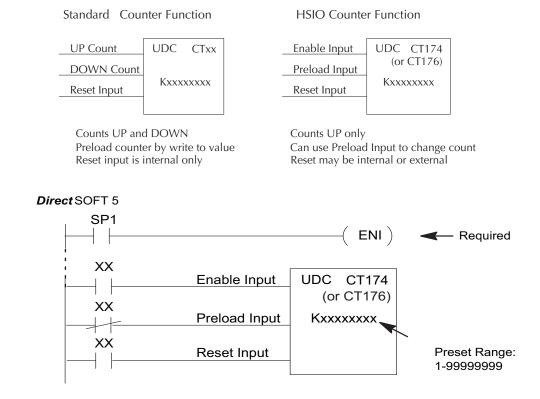

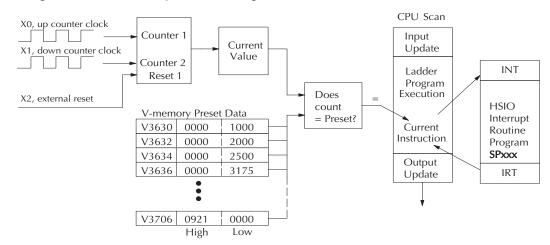

| Mode 10: High-Speed Counter                            |              |

| Purpose                                                |              |

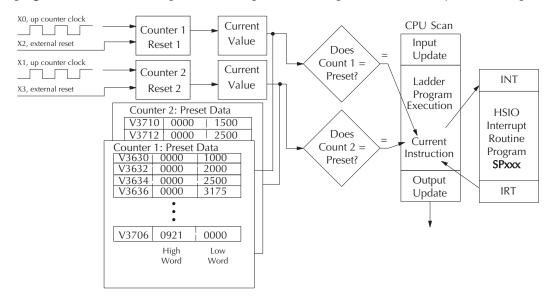

| Functional Block Diagram                               |              |

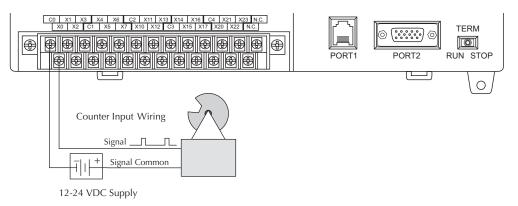

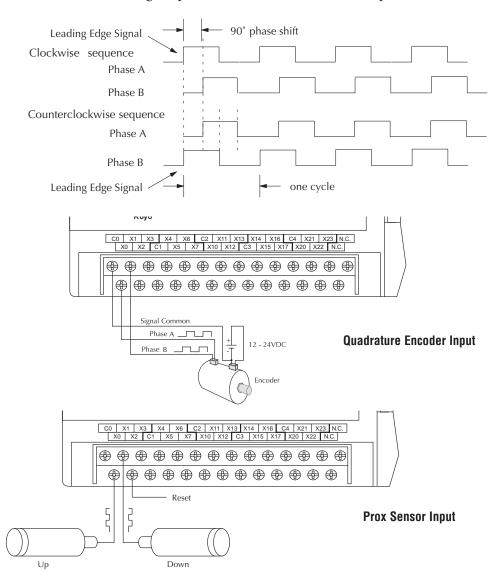

| Wiring Diagram                                         | E–8          |

| Interfacing to Counter Inputs                          | E–8          |

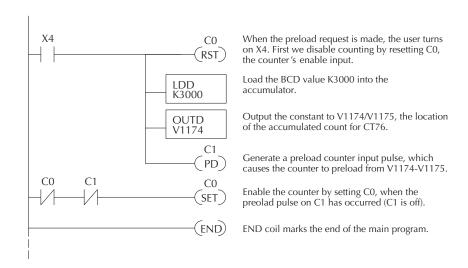

| Setup for Mode 10                                      | E–9          |

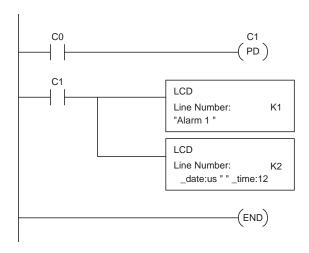

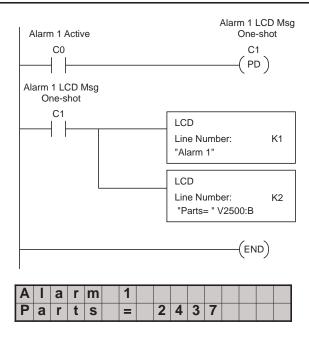

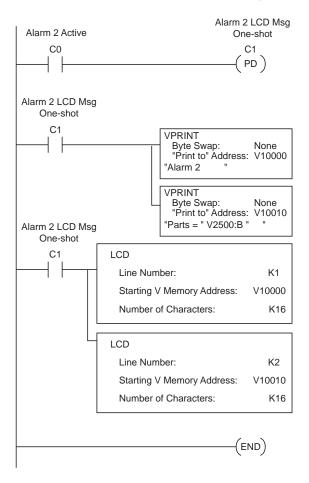

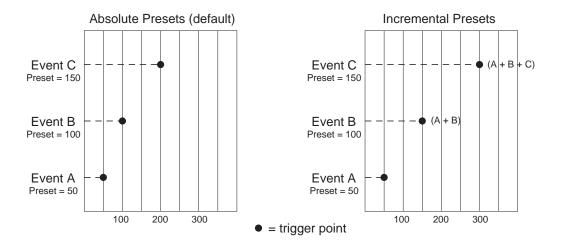

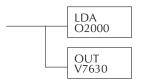

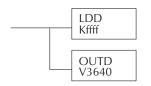

| Presets and Special Relays                             | E–9          |