# **Instruction Bulletin**

Local / Remote Inferface Class 8030 Types CRM-210, 211, 220 222 Bulletin # 30598-247-01D2 October, 1990

# == WARNING :

The application of this product requires expertise in the design and programming of control systems. Only persons with such expertise should be allowed to program, install, alter, and apply this product. Potential bodily injury, death, or equipment damage could result if the product is improperly applied to any equipment application.

# **CAUTION** ·

SY/MAX devices contain electronic components that are very susceptible to damage from electrostatic discharge. DO NOT handle this device by the gold edge contacts.

A static charge can accumulate on the surface of ordinary plastic wrapping or cushioning material. If any SY/MAX device must be returned to Square D, the following packaging instructions must be followed:

<u>PREFERRED:</u> Use the original packaging material as supplied by Square D. Place the device inside the metallized plastic bug.

ACCEPTABLE: Wrap the device in some type of antistatic material. Antistatic plastic material can be identified by its pink color, and can be obtained in sheet or bag form.

<u>UNACCEPTABLE</u>: Do not use ordinary plastic film, foam, or styrene chips ("popcorn" or "peanuts"). These materials can accumulate static charges in excess of 10,000 volts, resulting in possible damage to the SY/MAX electronic components.

Antistatic (metallized plastic) bags can be obtained from the following manufacturers:

- 3M Company (800-328-1368) Type 2100 bag

- Static, Inc. (800-782-8424) 8000 Series bag

- Charles Water (617-964-8370) CP-303 bag

# **CAUTION**

Improper handling may cause permanent damage to this device.

- Never remove this device from the rack while power is ON.

Turn power supply switch to OFF and wait until all indicating lights are off before removing.

- 2) Do not subject to static discharge.

- 3) Do not touch gold edge contacts.

# NOTICE

The products and services described in this manual are useful in a wide variety of different applications. Therefore, the user and others responsible for applying the products and services described herein are responsible for determining their acceptability for each application. While efforts have been made to provide accurate information within this manual, the Square D Company assumes no responsibility for the application, completeness or usefulness of the information contained herein.

UNDER NO CIRCUMSTANCE WILL THE SQUARE D COMPANY OR ANY OF ITS SUBSIDIARIES BE RESPONSIBLE OR LIABLE FOR ANY DAMAGES OR LOSSES, INCLUDING INDIRECT OR CONSEQUENTIAL DAMAGES OR LOSSES, ARISING FROM EITHER THE USE OF ANY INFORMATION CONTAINED WITHIN THIS MANUAL OR THE USE OF ANY PRODUCTS OR SERVICES REFERENCED HEREIN.

No patent liability is assumed by the Square D Company with respect to the use of any of the information, products, circuits, programming or services referenced herein.

The information contained in this manual is subject to change without notice.

# **TABLE OF CONTENTS**

| Section        | Title                                          | Page     |

|----------------|------------------------------------------------|----------|

| 1.0            | INTRODUCTION                                   | 5        |

| 1.1            | General Information                            | 5        |

| 1.2            | Summary of Operation                           | 5        |

| 2.0            | SPECIFICATIONS                                 | 6        |

| 2.1            | General Information                            | 6        |

| 2.2            | Electrical                                     | 6        |

| 2.2.1          | CURRENT DRAW                                   | 6        |

| 2.2.2          | CAPABILITIES                                   | 6        |

| 2.2.3          | COMPATIBILITY WITH PROCESSORS                  | 6        |

| 2.2.4          | COMPATIBILITY WITH RACKS                       | 6        |

| 2.2.5          | COMPATIBILITY WITH I/O                         | 7        |

| 2.3            | Environmental                                  | 7        |

| 2.4            | Physical                                       | 7        |

| 3.0            | INSTALLATION                                   | 7        |

| 3.1            | General Information                            | 7        |

| 3.2            | Inspection                                     | 7        |

| 3.3            | Module Keying                                  | 7        |

| 3.4            | Module Location                                | 8        |

| 3.4.1          | LOCAL INTERFACE                                | 8        |

| 3.4.2          | REMOTE INTERFACE                               | 8        |

| 3.5            | Field Wiring                                   | 8        |

| 3.5.1          | POWER CONNECTION                               | 8<br>8   |

| 3.5.2<br>3.5.3 | LOCAL/REMOTE CONNECTIONS                       | 8        |

| 3.5.3<br>3.6   | RI Switch Settings                             | 8        |

|                | -                                              |          |

| 4.0            | OPERATION                                      |          |

| 4.1            | General Description                            |          |

| 4.2            | Local Interface Registers                      | 9        |

| 4.2.1          | EXTERNAL REGISTERS                             | 10<br>10 |

| 4.2.2          | INTERNAL REGISTERS                             | 10       |

| 4.2.3          | CONTROL REGISTERS                              | 10       |

| 4.3            | Rack Addressing PROCESSOR (CPU) CONSIDERATIONS | 10       |

| 4.3.1<br>4.3.2 | ADDRESSING ASSIGNMENT AND DISTRIBUTION         |          |

| 4.3.2<br>4.3.3 | LI CONTROL REGISTER ALLOCATION                 | 10       |

| 4.3.5          | LI ADDRESSING WITH THE MODEL 300, 400, AND 600 | 13       |

| 4.3.6          | MULTIPLE LIS                                   | 13       |

| 4.4            | Summary                                        |          |

| 4.4.1          | HARĎWARE CONSIDERATIONS                        | 13       |

| 4.4.2          | SOFTWARE CONSIDERATIONS                        | 13       |

| 5.0            | TROUBLESHOOTING                                | 14       |

| 5.1            | General Information                            | 14       |

| 5.2            | General Procedures                             | 14       |

| 5.2.1          | CPU PROCESSOR MALFUNCTION                      | 14       |

| 5.2.2          | COMPONENT FAILURE                              |          |

| 5.2.3          | USER SOFTWARE PROGRAM ERROR                    | 14       |

| 5.3            | LI/RI LED Explanation                          | 14       |

| 5.4            | Isolation Procedures                           |          |

| 5.5            | Undervoltage Lockout Circuit (ULC) Operation   | 16       |

| 5.6            | Module Replacement Procedure                   | 16       |

| 5.7            | Li/Ri Communication Restart (Push Button)      | 16       |

| 5.7.1          | FROZEN DROP RESET                              |          |

| 5.8            | CPU and LI/RI Response to Faults               |          |

| 5.9            | Obtaining Additional Assistance                | 18       |

| APPENDIX | TITLE                           | PAGE |

|----------|---------------------------------|------|

| A        | LI/RI UPDATE TIME               | 19   |

| В        | ERROR CODES                     | 21   |

| C        | CHANNEL EXPANSION               | 29   |

| D        | LI CONTROL/STATUS REGISTERS     | 30   |

| Ē        | LI/RI POWER UP SEQUENCE         | 34   |

| F        | LI/RI ADDRESSING WITH MODEL 300 | 35   |

| G        | ADDITIONAL DATA LINE PROTECTION | 38   |

# LIST OF FIGURES

| Figure<br>Number | Description                                             | Page |

|------------------|---------------------------------------------------------|------|

| 1.1              | Local/Remote System                                     | 5    |

| 1.2              | Local Interface Features                                | 5    |

| 1.3              | Remote Interface Features                               | 5    |

| 2.1              | Maximum Channel Update Times (Digital I/O Only)         | 6    |

| 2.2              | Maximum Channel Update Times (Register and Digital I/O) | 6    |

| 2.3              | Model 300 Compatibility                                 | 6    |

| 2.4              | Rack Compatibility                                      | 7    |

| 3.1              | Module Keying                                           | 7    |

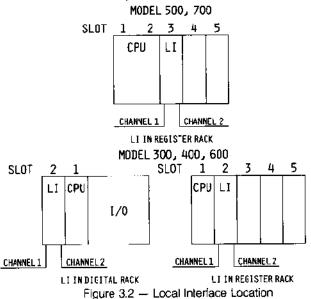

| 3.2              | Local Interface Location                                | 8    |

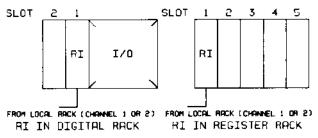

| 3.3              | Remote Interface Location                               | 8    |

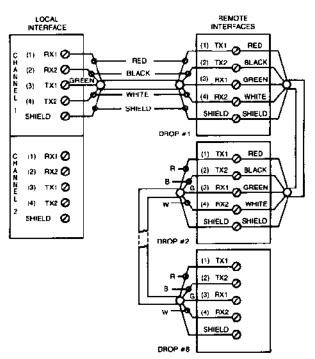

| 3.4              | LI/RI Wiring Connections                                | 8    |

| 3.5              | RI Switch Settings                                      | 9    |

| 3.6              | RI Module Labels                                        | 9    |

| 4.1              | CPU Address Capabilities                                | 10   |

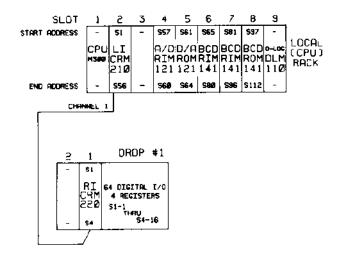

| 4.2              | Local (Model 500 CPU) Rack Address Assignments          | 11   |

| 4.3              | Channel I, Drop #1 Rack Address Assignments             | П    |

| 4.4              | Channel 1, Drop #2 Rack Address Assignments             | 11   |

| 4.5              | Channel 2, Drop #1 Rack Address Assignments             | 12   |

| 4.6              | LI Register Map                                         | 12   |

| 4.7              | Local (CPU) Rack Address with Multiple Lls              | 13   |

| 5.1              | LI LED Explanation                                      | 15   |

| 5.2              | RI LED Explanation                                      | 15   |

| 5.3              | LI/RI LED Response to Errors                            | 16   |

| 5.4              | CPU and LI/RI Response to Remote I/O Faults             | 17   |

| 5.5              | Equipment List                                          | 18   |

| A.I              | Digital Channel.                                        | 19   |

| A.2              | Register Channel                                        | 19   |

| B. l             | A Typical P.C. System                                   | 27   |

| D. I             | LI Control/Status Register Assignments                  | 30   |

| D.2              | LI Control Data Register                                | 31   |

| D.3              | LI Control Status Register                              | 32   |

| F. 1             | Local (Model 300 CPU) Digital Rack Address Assignments  | 35   |

| F.2              | Channel 1, Drop #1 Rack Address Assignments             | 35   |

| F.3              | Channel 1, Drop #2 Rack Address Assignments             | 35   |

| F.4              | Channel 2, Drop #1 Rack Address Assignments             | 36   |

| F.5              | Local (Model 300 CPU) Register Rack Address Assignments | 36   |

| F.6              | Channel 1, Drop #1 Rack Address Assignments             | 37   |

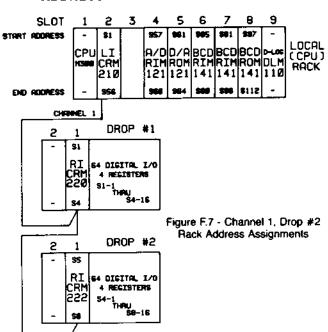

| F.7              | Channel 1, Drop #2 Rack Address Assignments             | 37   |

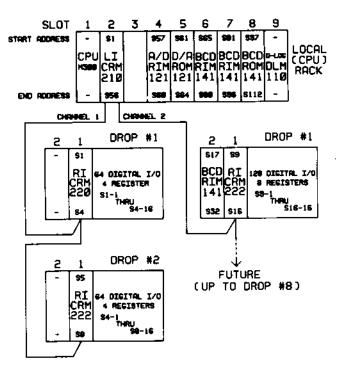

| F.8              | Channel 2. Drop #1 Rack Address Assignments             | 37   |

## 1.0 INTRODUCTION

# 1.1 General Information

The local and remote interface (LI and RI) system for the SY/MAX programmable controller Family provides a versatile method of handling a wide variety of local and remote I/O and register module configurations. It has the interfacing capability to handle everything from the smallest single task machines to systems requiring thousands of remote I/O and register functions.

This bulletin provides the basics to configure a remote I/O system to meet a PC system design needs with a minimum of hardware, thereby reducing the total cost and time required for implementation of the control scheme.

# 1.2 Summary of Operation

By utilizing the SY/MAX LI and RI modules, both digital and register racks can be located remotely from a SY/MAX processor. The modules allow communication with the processor over a two pair, twisted, shielded cable, greatly reducing the cost of control wiring to the remote electrical inputs and outputs.

To establish a remote I/O system, an LI module is mounted in the rack containing the processor and an RI module is mounted in the remote rack (referred to as a drop). The dual twisted shielded pair cable is connected to a removable terminal strip on the face of each module.

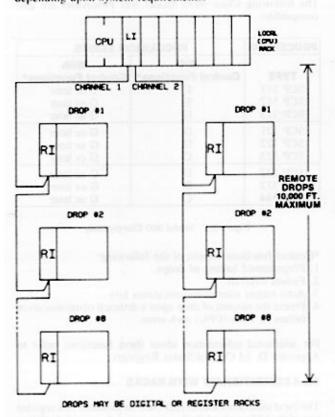

As shown in Figure 1.1, the LI module has two communication channels. Each channel may consist of a chain of up to 8 drops (digital or register racks). More than one LI module may be used with many of the SY/MAX Family processors, depending upon system requirements.

Figure 1.1 - Local/Remote System

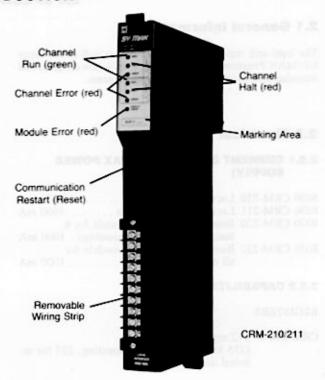

Figure 1.2 - Local Interface Features

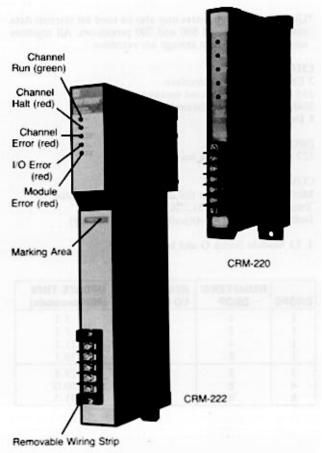

Figure 1.3 - Remote Interface Features

# 2.0 SPECIFICATIONS

# 2.1 General information

The local and remote interface modules, as well as the entire SY/MAX Programmable Controller Family, are designed and manufactured to comply with U.L. requirements.

# 2.2 Electrical

# 2.2.1 CURRENT DRAW (ON SY/MAX POWER SUPPLY)

|              | Local w/512 Registers 1600 mA<br>Local w/4096 Registers 1600 mA              |

|--------------|------------------------------------------------------------------------------|

|              | Remote (low profile module for 4                                             |

| 8030 CRM-222 | function digital rack mounting). 1000 mA<br>Remote (standard size module for |

|              | all rack mounting), 1000 mA                                                  |

#### 2.2.2 CAPABILITIES

#### REGISTERS

CRM-210 = 512 registers

(255 for external drop addressing, 257 for internal data storage\*)

CRM-211 = 4096 registers

(255 for external drop addressing, 3841 for internal data storage\*)

#### CHANNELS

2 Channels per local interface.

255 Registers per channel maximum.

2048 Digital I/O per channel maximum.

8 Drops per channel.

# DROPS

127 Registers per drop maximum.

# COMMUNICATIONS

Method — Continuous full duplex serial differential Transmission Rate — 31.25K Baud Isolation — 300VDC optically coupled (LI only)

t. LI Module Series O and later only.

| DROP\$ | REGISTERS/<br>DROP | AVAILABLE<br>I/O POINTS | UPDATE TIME<br>(Milliseconds) |

|--------|--------------------|-------------------------|-------------------------------|

| ı      | <br>               | 16                      | 5.1                           |

| 1      | 2                  | 32                      | <b>7</b> . l                  |

| l      | 4                  | 64                      | 11.1                          |

| l t    | 8                  | 128                     | 19.1                          |

| 2      | - 8                | 256                     | 29.4                          |

| 4      | 8                  | 512                     | 50.0                          |

| 8      | 8                  | 1024                    | 91.3                          |

Figure 2.1 Maximum Channel Update Times (Digital I/O Only)

| DROPS                 | REGISTERS/<br>DROP | TOTAL<br>REGISTERS | UPDATE TIME<br>(Milliseconds) |

|-----------------------|--------------------|--------------------|-------------------------------|

| J                     | 4                  | 4                  | 14.6                          |

| 1                     | 8                  | 8                  | 24.5                          |

| 1                     | 16                 | 16                 | 34.4                          |

| 1                     | 32                 | 32                 | 54.3                          |

| 1                     | 64                 | 64                 | 94.0                          |

|                       | 127                | 127                | 172.1                         |

| 2                     | 8                  | 16                 | 36.0                          |

| 2<br>2<br>2<br>2<br>2 | 16                 | 32                 | 55.8                          |

| 2                     | 32                 | 64                 | 95.5                          |

| 2                     | 64                 | 128                | 166.5                         |

| 2                     | 127                | 254                | 332.7                         |

| 4                     | 16                 | 64                 | 103.4                         |

| 4                     | 32                 | 128                | 182.8                         |

| 4                     | 64                 | 254                | 341.5                         |

| 6                     | 16                 | 96                 | 220.4                         |

| 6                     | 32                 | 192                | 260.4                         |

| 8                     | 16                 | 128                | 195.4                         |

| 8                     | 32*                | 255                | 352.9                         |

<sup>\*</sup> One drop has only 31 registers.

Figure 2.2 - Maximum Channel Update Times (Register and Digital I/O)

## 2.2.3 COMPATIBILITY WITH PROCESSORS

The local remote interface system is compatible with all Model 400, 500, 600 and 700 SY/MAX Processors. Multiple LIs may be used with Models 400, 500, 600 and 700. The Model 300 can support one LI Module.

The following Class 8030 Model 300 Processors are also compatible:

| PROCESSOR | PROCESSOR SERIES          |                            |  |  |  |  |  |  |

|-----------|---------------------------|----------------------------|--|--|--|--|--|--|

| TYPE      | W/O<br>Control Functions* | With<br>Control Functions* |  |  |  |  |  |  |

| SCP 311   | Е                         | G or later                 |  |  |  |  |  |  |

| SCP 312   | E                         | G or later                 |  |  |  |  |  |  |

| SCP 313   | D                         | G or later                 |  |  |  |  |  |  |

| SCP 321   | D                         | G or later                 |  |  |  |  |  |  |

| SCP 322   | D                         | G or later                 |  |  |  |  |  |  |

| SCP 323   | C                         | G or later                 |  |  |  |  |  |  |

| SCP 332   | D                         | G or later                 |  |  |  |  |  |  |

| SCP 333   | D                         | G or later                 |  |  |  |  |  |  |

| SCP 344   | С                         | G or later                 |  |  |  |  |  |  |

Figure 2.3 - Model 300 Compatibility

- \*Control functions consist of the following:

- 1. Programmed halting of drops.

- 2. Failure override.

- 3. Auto restart after communications loss.

- Freeze the outputs of drop upon a detected communication failure or local (CPU) rack error.

For additional information about these functions, refer to Appendix D, LI Control/Status Registers.

# 2.2.4 COMPATIBILITY WITH RACKS

The local interface module (LI) must be mounted in a register slot of the CPU rack while the remote interface module (RI) is mounted into the CPU slot of a remote rack.

<sup>\*</sup>Unused external registers may also be used for internal data storage in the model 500 and 700 processors. All registers used for internal data storage are retentive.

| RACK                                         | LOCAL INTERFACE    | REMOTE INTERFACE |              |  |  |  |

|----------------------------------------------|--------------------|------------------|--------------|--|--|--|

| TYPES                                        | TYPES CRM-210, 211 | Type CRM-220     | Type CRM-222 |  |  |  |

| CRK-100, 210                                 | NO                 | YES              | YES          |  |  |  |

| CRK-210, 300<br>DRK-210, 300<br>GRK-110, 210 | YES                | YES              | YES          |  |  |  |

| HRK-100, 150, 2<br>RRK-100, 200, 3           | 00 YES             | NO               | YES          |  |  |  |

Figure 2.4 - Rack Compatibility

# 2.2.5 COMPATIBILITY WITH I/O

The local/remote interface system is compatible with:

All register modules.

All 32 point 1/O modules.

All 16 point I/O modules.

All 8 point 1/O modules.

All 4 point input modules.

All 4 point output modules, Series B or later.

Bus Expander, Class 8030 Type CRM-115/116, Series D or

# 2.3 Environmental

Ambient Temperature

Operating 0°C to 60°C (32° to 140°F)

Storage -40°C to 80°C (-40° to 176°F)

Humidity 5-95% non-condensing

# 2.4 Physical

Dimensions (WxHxD)

CRM-210, 211, 222 1.5 x 12.8 x 6.6 in.

3.81 x 32.5 x 16.76 cm

CRM-220 ...... 1.5 x 9.6 x 6.6 in.

3.81 x 24.4 x 16.76 cm

Weight

CRM-210, 211, 222 3.0 lbs. 1.36 kg. CRM-220 . . . . 1.0 lb. 0.45 kg.

Terminal strips

CRM-210, 211 .... Part Number 25410-02529 CRM-220 .... Part Number 30605-255-02 CRM-222 .... Part Number 25410-02526

## 3.0 INSTALLATION

# 3.1 General Information

CAUTION: To prevent possible equipment damage, remove power from all local and remote racks before inserting or removing any component including the interface modules or LI/RI communication cables.

Local Interface Modules identified as Series L or later incorporate diagnostic enhancements not available in earlier series devices. Expanded error checking of data registers will return a unique error code (901) in the event a data corruption is determined. When initially replacing or installing a new Local Interface (LI), the user should expect the posting of this error as a normal "out of the box" condition. After installing the device and powering up the system, upon initially keyswitching the processor to DISABLE OUTPUTS or RUN, the processor will remain in HALT and the LI will indicate a MODULE ERROR. The processor error register (8175) will identify the LI in error while the LI error register will contain the value 901. This is a normal occurrence, reflecting the fact that the LI storage registers are corrupt (contain random data). Key Switching the processor a second (or third) time will result in all LI registers being reset to zero and the error being cleared. Normal operation will then result.

# 3.2 Inspection

Although each module is subjected to strict quality control procedures, give each module a visual inspection before installation. Check for any shipping or handling damage that may have occurred. If damage is found, do not use the module, replace it.

# 3.3 Module Keying

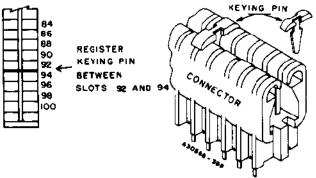

Each register or CPU slot on a rack assembly may be keyed. An optional keying pin kit, Class 8030 Type CBP 104, is available for this purpose.

The keying pin may be inserted manually into the slot using the keying pin insertion tool provided with the kit.

The correct positioning of the keying pin for the LI and RI modules follows:

# TYPE DESCRIPTION PIN LOCATION CRM-210 Local Interface (LI) Module w/512 Registers Between 92 & 94 CRM-211 Local Interface (LI) Module w/4096 Registers Between 92 & 94 CRM-220 Remote Interface (RI) Module (for 4 function digital racks) CRM-222 Remote Interface (RI) Module (for all type rack assemblies)

Keying Pin Location

**Keying Pin Insertion**

Figure 3.1 - Module Keying

# 3.4 Module Location

# 3.4.1 LOCAL INTERFACE

The local interface module (LI) must be placed in the same rack assembly as the CPU. When a register rack is used to house the CPU, the LI module should be placed in the next closest slot. If more than one LI module is required, place additional modules in adjacent slots.

## 3.4.2 REMOTE INTERFACE

The remote interface module (RI) must be placed into the CPU slot of any rack which is to be a drop.

Only one RI is required and allowed for each drop.

Figure 3.3 - Remote Interface Location

# 3.5 Fleld Wiring

## 3.5.1 POWER CONNECTION

No external power wiring is required. The LI and RI modules receive their power through the edge connector socket of the rack assembly. Insert the LI module in the register slot until firmly seated against the stud (the middle post above the socket in that slot) and tighten the captive mounting screw at the bottom of the module. These two connections not only provide support for the module but also provide a ground.

# 3.5.2 COMMUNICATION CABLE

The communication between the LI and RI modules is achieved via a dual shielded twisted pair cable. A hinged plastic flap covers the detachable terminal strip. In order to minimize the potential of electrical interference:

Route communication cable in different wire ducts than the power wiring is routed. 2 Connect each end of the communications cable shield to the shield terminal on each module.

Transmission cable should be electrically equivalent to:

|                   | Maximum     | Conductor-<br>Conductor |

|-------------------|-------------|-------------------------|

| Cable Type        | Length      | Capacitance             |

| Belden 8723       | 7,500 feet  | 35 pf/ft.               |

| Belden 9463*      | 10,000 feet | 19.7 pf/ft.             |

| *Dual cables requ | uired.      | •                       |

# NOTE: ADDITIONAL DATA LINE PROTECTION

In environments where lightning or induced transients over communication lines are likely to cause hardware failures, signal line protection devices are recommended. Even though transient protection is designed into our SY/MAX communication circuits, additional specialized protection devices are suggested in areas where there is a high probability of secondary lightning strikes occurring. The specific environments which are of greatest concern are where communication cable runs are in the outside environment. Refer to Appendix G.

#### 3.5.3 LOCAL/REMOTE CONNECTIONS

The required method of wiring from one module to the next is daisy chain. Since the LI/RI is designed to operate as a serial link, any configuration other than daisy chain may result in erratic operation. Total allowed cable distance for each channel when using Belden 8723 is 7,500 ft.

Figure 3.4 - Ll/Rl Wiring Connections

# 3.6 RI Switch Settings

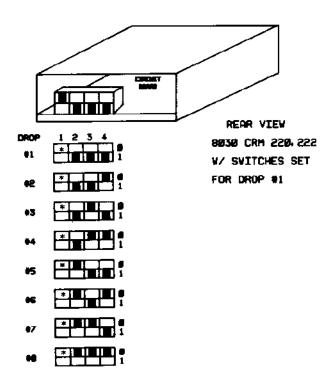

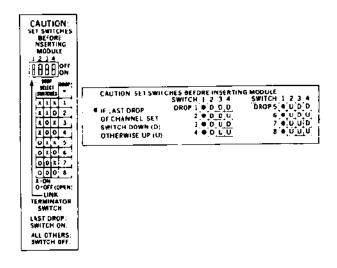

The RI Module has four dip switches on the rear of the module near the edge of the circuit board. A module must be assigned as one of the eight drops on a specific channel. The switches must be set for the system to operate properly.

Set the switches for the appropriate drop as shown in Figure 3.5 - RI switch settings.

<sup>\*</sup>For each channel, the drop (RI module) farthest from the LI must have switch 1 set ON, to a (1). Only one drop per channel requires this switch to be set. Failure to do so may result in a noise susceptible communications link.

Figure 3.5 - RI Switch Settings

Label terminology may vary. The following equivalent terms are used:

| 0 | 0 | UP   | OPEN   | OFF |

|---|---|------|--------|-----|

| 1 | X | DOWN | CLOSED | ON  |

Either one of these labels will be located on the side of the RI module.

Figure 3.6 - RI Module Labels

# 4.0 OPERATION

# 4.1 General Description

Local and remote interface modules allow a programmable controller to communicate with remote I/O (digital and register input and output type devices).

The LI/RI interface system consists of:

- A local interface module (LI) which plugs into a register slot of the rack containing the CPU.

- A remote interface module (RI) placed in the CPU slot of a digital I/O rack or the first slot of a register rack.

- An interconnecting cable between the LI and R!(s) consisting of dual twisted shielded pair.

Both the LI and RI modules have diagnostic LED's indicating the status of the communication link, individual drop operation and module operation.

The local/remote I/O interface system is a serial, multichannel, multi-drop system. The local interface (LI) receives instructions from the CPU. The LI then serializes this information and transmits it to the appropriate remote interface (RI). An LI module does this over either of its two independent communication channels. Each channel operates full duplex at a rate of 31.25K baud. The RI interprets this data, verifies and acknowledges it and then acts accordingly. The information being exchanged is stored in an image table located in each LI and RI.

The continuous exchange of information between the LI and RI image tables is independent of the CPU scan. Transmitted information includes ON/OFF commands for I/O as well as storage register information and housekeeping functions (e.g. loss of communications, error control, freeze or reset of I/O).

The LI module stores control register information while the RI maintains its own specific drop information. This information (user programmable bits) defines the action to be taken in the event of a fault at any drop. It can allow the operational drops to keep running or to shutdown. The shutdown state of the outputs will then be either a reset (OFF) or freeze (last state) condition.

Actual programming steps are described in the programming equipment instruction bulletins. For details on user programmable bits, refer to Appendix D, LI Control/Status Registers.

# 4.2 Local Interface Registers

Two versions of the LI module are available. The first, Class 8030 Type CRM-210, has 512\* registers; and the second,

Class 8030 Type CRM-211, has 4096\* registers. With either version LI, the first 255\*\* registers are available for external addressing of inputs, outputs, register modules, storage registers or as internals. The remaining registers (257 for CRM-210, or 3841 for CRM-211) are available for use as internal relay equivalents, timers, counters, and data storage in the Model 500 and 700.

- \*Although the registers exist, the ability to address them is dependent upon the type of CPU used.

- \*\*Any of the 255 registers not assigned to drops may be used as internals for the Model 500, 700.

#### **4.2.1 EXTERNAL REGISTERS**

A maximum of 255 consecutive registers can be assigned between the two independent LI channels. Each LI channel can support up to 8 drops. (A drop is a remotely located rack assembly.) Any drop may have a maximum of 127 registers assigned to it. The first 8 registers assigned to a drop are available for digital or register I/O. (e.g. 8 registers x 16 bits provide for 129 I/O points per drop.) Any registers beyond the first 8 are only for register I/O.

The registers assigned to drops will be reset to zero (OFF) upon processor halting or power loss. However, it is possible to freeze (maintain last state) registers assigned to drops. For more information, refer to Appendix D, LI Control/Status Registers.

# **4.2.2 INTERNAL REGISTERS**

Internal registers (those not assigned to drops) retain information when the processor halts or there is a loss of main power. The clearing of these registers is dependent upon processor action.

# 4.2.3 CONTROL REGISTERS

All LI modules have an error code register and a channel control register for each serial channel. These registers monitor and provide additional control of the remote I/O. For more information, refer to Appendix B, Error Codes and Appendix D, LI Control/Status Registers.

# 4.3 Rack Addressing

Rack Addressing (also referred to as System Definition) is a user programmable identification scheme that enables a SY/MAX Processor to obtain information about a specific I/O point or register

It maps the physical location of where the processor (CPU) will "look" for a specific address and its associated information when required.

Once the register addresses have been assigned, they are fixed. If a change in address assignments is required, the user rack addressing software must be changed.

## 4.3.1 PROCESSOR (CPU) CONSIDERATIONS

The CPU determines the maximum system addressing range. SY/MAX Processor capabilities are as shown in Figure 4.1.

# 4.3.2 ADDRESSING ASSIGNMENT AND DISTRIBUTION

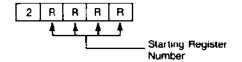

All address assignments must be made in a sequential and ascending order. The first 255 LI registers may be assigned to channel 1 and then to channel 2. Each of these channels can be further divided into 8 drops. The register addresses for each drop may be further distributed in ascending order to individual slots of the remote drops.

Internal addresss begin after external addresses have been assigned. Internal and external registers cannot be intermixed.

## 4.3.3 LI CONTROL REGISTER ALLOCATION

LI control registers are dynamically assigned on the basis of physical position and rack addressing.

- LI control registers are assigned in a descending order starting with S8163 for the LI with the lowest numbered CPU rack slot number.

- LI control registers are further defined by the number of channels used.

For example, if only channel 1 is assigned to the first L1, there will be no control register assigned to channel 2, S8163 is the error code control register, S8162 is the channel control register for channel 1, S8161 is left unassigned.

If an additional L1 is put in a higher numbered CPU slot, it would be assigned the *next* available control register, i.e., \$8161 becomes the second L1 error code register. \$8160 is the control register for channel 1 of the second L1. \$8159 is unassigned and available for channel 2 or for a third L1's error code register. If only channel 2 is defined, the system automatically assigns a control register to channel 1 whether channel 1 is used or not.

For more information on the operation of the L1 control registers, refer to Appendix B, Error Codes and Appendix D, L1 Control/Status Registers.

| CPU<br>Model | Register<br>Addressing<br>Capability | Self Contained<br>CPU Registers | Maximum<br>Supportable<br>Li Modules | Practical<br>I/O Capability |

|--------------|--------------------------------------|---------------------------------|--------------------------------------|-----------------------------|

| 300          | 112 (1)                              | 112                             | 1                                    | 256                         |

| 500          | 2008 (2)                             | 460 (3)                         | 14                                   | 2000                        |

| 700          | 8000 (2)                             | 0 ` ′                           | 14                                   | 8000                        |

| 400          | 4000                                 | 4000                            | 15                                   | 4000                        |

| 600          | 8000                                 | 8000                            | 15                                   | 8000                        |

- Only the hits of the first 32 registers may be forced ON/OFF.

- (2) Only the bits of the first 256 registers in each LI may be forced ON/OFF.

- (3) For internal use only as relays and storage registers.

#### 4.3.4 LI/RI ADDRESSING WITH MODEL 500

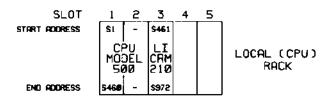

The following example is used to illustrate the concept of address assignment.

This example consists of a Model 500 system with two remote I/O channels. The first channel handles 256 digital I/O points and one register module. Two remote drops are used to handle these requirements. The second channel consists of a register rack with 5 register modules.

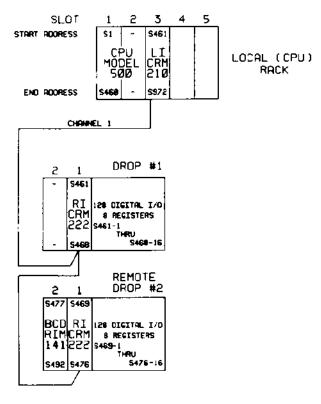

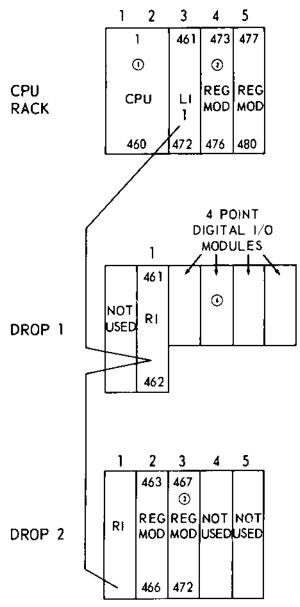

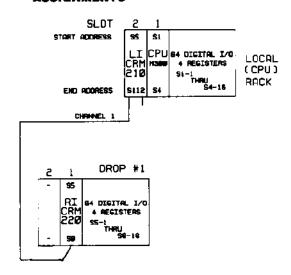

Figure 4.2 - Local (Model 500 CPU) Rack Address Assignments

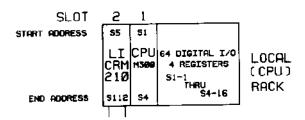

# LOCAL (CPU) RACK

- Slot 1 The Model 500 has been assigned all of its 460 internal registers. (\$1 thru \$460)

- Slot 2 The Model 500 physically takes up two slots therefore, slot 2 has no address assignments required.

- Slot 3 The LI module (CRM-210) has been assigned all of its 512 registers. (S461 thru S972)

- Slot 4, 5 No address assignments required.

Assigning all available registers to the CPU and LI does not affect the CPU scan. Note that the first register of the LI has a start address of \$461, one more than the assigned end address of the processor. The LI end address is \$972 which is 512 more than the end address of the processor.

Note that the start and end addresses of the system slots are shown. However, when programming addressing assignments, only ending addresses can be entered. Starting addresses are automatically assigned beginning with the next available register. For a full explanation of the step by step rack addressing programming procedure, refer to the SFW-3XX Programming Instruction Bulletin.

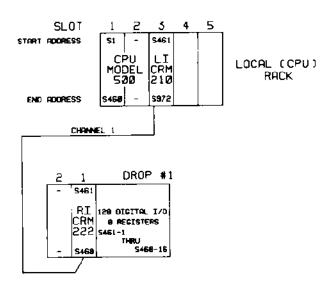

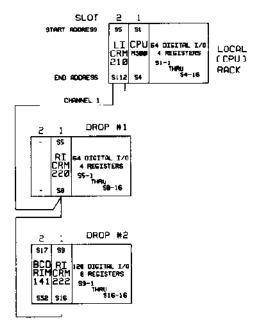

Figure 4.3 - Channel 1, Drop #1

Rack Address Assignments

# CHANNEL 1, DROP #1

Slot 1 - To handle 128 digital I/O points, 8 - 16 bit registers are required. (\$461-1 thru \$468-16)

Note that the addresses for digital  $\nu O$  are always assigned to slot L.

Slot 2 - No address assignments required.

#### CHANNEL 1, DROP #2

The next order of business is to add another drop to an already existing channel. This drop also has 128 digital I/O points but unlike drop #1, it has a register module. The module is in the register slot, (slot 2) which requires 16 register addresses.

- Slot 1 8 registers are assigned for the 128 digital I/O. (\$469-1 thru \$476-16).

- Slot 2 16 registers are required for the register module. (S477 thru S492).

The total requirement for this drop is 24 registers. Observe that the start address for drop #2 is one more than the end address for drop #1. The first digital address for drop #2 is S469-1 and the last digital address is S476-16. Therefore, slot 1 has an ending register address of S476. Slot 2 ends at S492, allowing for the required 16 registers needed by the register module.

This process of adding a drop at a time in a daisy chain fashion could be continued until all 255 registers were assigned to a channel or until all 8 drops had been assigned.

Figure 4.4 - Channel 1, Drop #2 Rack Address Assignments

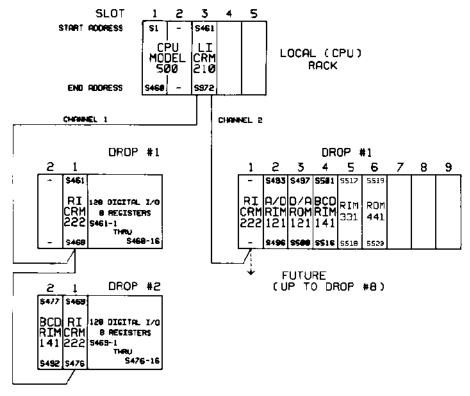

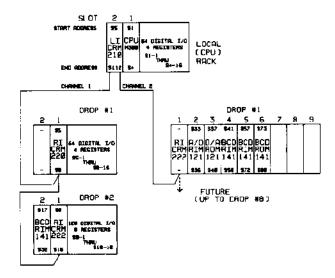

Figure 4.5 - Channel 2, Drop #1

Rack Address Assignment

# **CHANNEL 2, DROP #1**

In this example, a 9 slot register rack is connected to channel 2.

Note that the starting address for channel 2 is one greater than the ending address of channel 1. In other words, when channel 1 ends, channel 2 begins.

Requirements for register modules vary. As an example, a 4 channel analog module requires 4 registers for complete addressing. A BCD I/O module requires 16 registers and a 32 point I/O module requires 2 registers each.

- Slot 1 No address registers are required since there is no digital I/O bus in the register rack. (The 32 point ditigal I/O modules appear as another register module to the LI.)

- Slot 2 4 registers are assigned to a 4 channel analog input module. (S493 thru S496)

- Slot 3 4 registers are assigned to a 4 channel analog output module. (\$497 thru \$500)

- Slot 4 16 registers are assigned to a 16 (4 digit) BCD input module. (S501 thru S516)

- Slot 5 2 registers are assigned to a 32 point digital input module. (S517 and S518)

- Slot 6 2 registers are assigned to a 32 point digital output module. (S519 and S520)

Slot 7,8,9 - No address assignments required.

The total number of registers required for this drop is 28. Note the beginning and ending addresses for each slot are sequential and in ascending order.

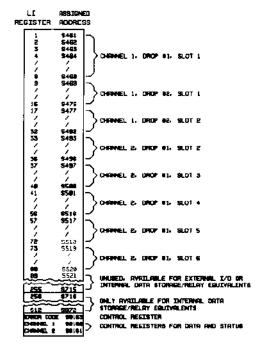

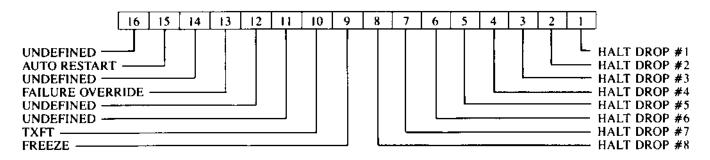

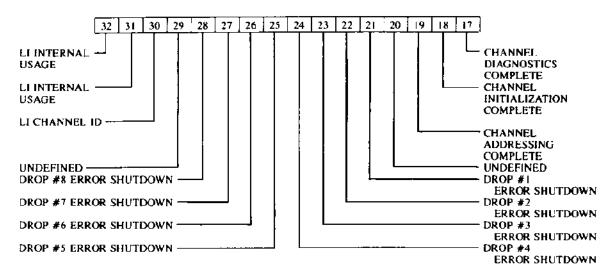

## LI ADDRESS DISTRIBUTION MAP

Here is a map of how the first LI has been user programmed in this example.

Observe that the LI has a fixed number of registers and rack addressing has assigned a unique address to each one.

Figure 4.6 - LI Register Map

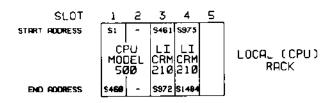

# 4.3.5 LI ADDRESSING WITH THE MODEL 300, 400 AND 600

As Figure 4.1, CPU Addressing Capabilities shows, the Model 300, 400 and 600 processors differ from the Model 500 and 700 in the area of self-contained CPU registers. All of the registers available to the Model 300, 400 and 600 are self-contained. In other words, it is unnecessary to Rack Address storage registers to modules like the LI as in a Model 500 or 700 system. When creating rack addressing for a Model 300, 400 or 600 system, only assign the number of register required for current and future remote drops. While it is valid to assign additional registers to the LI, it may reduce overall system throughput.

As an example, the Rack Addressing presented in the previous section for a Model 500 system can be used, as is, for a Model 400 or 600 system. But in order to optimize the system, only those registers required for remote drops (\$461 \$520) should be assigned to the LI. All other registers (\$521-\$4000 for the Model 400 or \$521-\$8000 for the Model 600) would still be available for storage. Because the Model 300 has only 112 registers available, the Rack Addressing presented in the previous section would not apply. Refer to Appendix F for additional information on Rack Addressing with a Model 300.

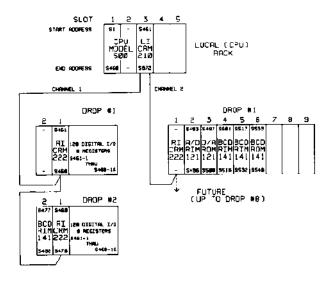

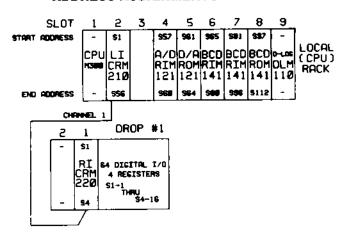

# 4.3.6 MULTIPLE LIS

If more drops or registers are required than those that can be supported by the present LL, merely add an additional LL module.\*

An LI module only provides storage register locations to a processor which possesses the capability to address them. The LI module does not increase the CPU addressing range capability.

Figure 4.7 - Local (CPU)

Rack Addresses with Multiple LIs

LI control register assignments are dependent upon LI position and number of channels used.

\*The number of LIs per system is CPU dependent, the Model 300 will support only one LI Module.

# 4.4 Summary

These steps should be looked at prior to setting up any LI/RI system.

- Sketch out the physical system configuration, (rack assemblies, power supplies, I/Os, etc.).

- Determine the address allocations based upon requirements of the system.

- Consider the system response time. Refer to Appendix A. Ll/R1 Update Time.

## 4,4.1 HARDWARE CONSIDERATIONS

- 1. Determine the physical I/O requirements including future expansion. (Quantity, voltages, racks)

- Determine I/O locations and number of drops required as well as I/O per drop.

- Determine the type of register modules required, including future expansion.

- Determine the location of register modules, quantity, and types of racks required.

- All modules used with the local/remote interfaces must be of compatible series.

- Communications devices should be powered down when connecting and disconnecting communication cabling. If a communication wire were to be shorted, premature chip failure may result.

- The LI module is always installed in the local CPU rack assembly.

- The RI module is always installed in slot 1, the CPU slot of the remote drop.

## 4.4.2 SOFTWARE CONSIDERATIONS

CAUTION: Only qualified personnel should ever program or implement action which may override the default system operations. A thorough understanding of the control bits is required. If any control bits are misapplied, adverse consequences may result.

- Any detected system error will result in the system halting. However, it is possible to override the halting of the total system when an error is in the remote location, dependent upon the severity of the error detected.

- 2. All digital I/O address on a drop must be assigned to slot 1.

- No registers need be assigned to slot 1 of a register rack used as a drop.

- 4 Register Planning

Register and I/O distribution for present and future needs should be considered prior to attempting any register address allocation (rack addressing).

For effective distribution of register addresses:

- A. Distribute external addresses evenly among channels. This allows for a uniform LI/R1 update time.

- B. Examine the LI/RI update time. If it is too long, add an additional LI module to obtain more channels. This will reduce the number of registers per channel. For more detail, refer to Appendix A, LI/RI Update Time.

Determine the CPU's ability to access the registers in the LI. For more information, refer to Figure 4.1 and the appropriate processor instruction bulletin. Remote drop addressing must be done sequentially. Therefore, plan to add future remote drops to channel 2.

For more information, refer to Appendix C, Channel Expansion.

CPU will go into the RUN mode only if all the drops are operational. Note that a drop may be made to appear operational by setting a channel control register Failure Override Bit ON (1). For more information, refer to Appendix D. I.I. Control/Status Registers.

## 5.0 TROUBLESHOOTING

#### 5.1 General Information

This section explains the procedures for troubleshooting the local and remote interface (LI/RI) system. Following the outlined procedures will aid in evaluating a malfunctioning system.

# 5.2 General Procedures

Always do the following:

- Examine and note what the system is doing and has failed to do.

- Examine and note the LED states on the LI/RI interfaces. (Refer to Figure 5.1 and Figure 5.2, LI and RI LED Explanation.)

- Using a Programmer, examine and note the control register information. (Refer to Appendix D, LI Control/Status Registers.)

There are three primary types of malfunctions which can occur within the SY/MAX Family LI/RI systems.

- 1. A CPU processor malfunction.

- 2. Component failure.

- 3. User software program error.

#### 5.2.1 CPU PROCESSOR MALFUNCTION

If a CPU processor malfunction is suspected, refer to the appropriate processor and CRT programmer instruction bulletins for further troubleshooting procedures.

If, however, it appears the problem may be related to the LI/RI system or user control program software, continue in this section.

# **5.2.2 COMPONENT FAILURE**

Besides the CPU, the malfunctioning of the following hardware components may cause the PC system to halt or continue to run in a partial mode.

> LI MODULES RI MODULES REGISTER MODULES I/O MODULES RACK ASSEMBLY POWER SUPPLY

Also, the system may halt if there is a lack of, or insufficient power at any location or a communication error.

Before replacing any hardware items, verify the problem by interpreting the LEDs and control register information.

#### 5.2.3 USER SOFTWARE PROGRAM ERROR

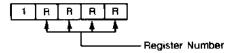

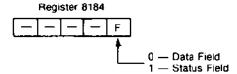

A CRT programmer is helpful in analyzing Ll/RI problems whether they are user created or system malfunctions. Use the monitor mode to display the following registers:

- 8175 processor error code register. (data & status field)

- 8176 processor control register. (data field)

- 8186 processor read only status control register. (data field)

- 8163 first LI Error Code Register. (data & status field)

- 8162 first L1 channel 1 Control/Status Register. (data & status field)

8161 - first LI channel 2 Control/Status Register. (data & status field)\*

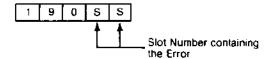

Note: The error code registers only display the most critical error detected prior to a total system shutdown. An error code may indicate either a specific register problem or it may be indicating the first register address of a block of registers where a problem has been detected.

Progressively inspecting all of the available CPU and LI control registers will aid in pinpointing the trouble area. Inspection of the channel control register data field (bits 1-8) will indicate what racks are halted due to the user program initiated control action while the status field will display the errored drops (bits 21-28).

\*For more information, refer to Section 4.3.3 LI Control Register Allocation.

# 5.3 LI/RI LED Explanation

For a normally operating system, all of the associated CPU, LI and RI modules should have their RUN LED's illuminated. When a detected system change occurs, the LED's indicate the status of the system. If an error has occured, it will also indicate where the error most likely originated.

However, if any of the RUN LEDs are off, it does not necessarily indicate that a system malfunction has occurred. The system could be in some mode of operation other than RUN such as DISABLE OUTPUTS, or even a HALT condition by virtue of the user program.

In most cases, inspection of the LEDs will directly indicate the status of each communications link and "point" to the error source.

The meaning of the LI and RI modules LED states is depicted in figures 5.1 and 5.2.

If it is impractical to view all the diagnostic LEDs or if they do not readily indicate where the failure has originated, inspection of the error code registers of the CPU and LI will aid in finding a fault.

General error code register information is described in Appendix B, Error Codes.

# 5.4 Fault Isolation Procedures

Note what the system is doing by examining the following:

## 1. LEDs

Determine which of the following LEDs are ON, FLASH-ING, or OFF.

- A. CPU (system processor)

- B. LI

- C. RI

## 2. Error Registers

Determine the contents of the Error Code and Control Registers.

- A. CPU (system processor register S8175)

- B. LI register (i.e. S8163 for the first LI in a system) refer to Appendix B, Error Codes for further information.

# LOCAL INTERFACE All lights OFF indicates loss of 5VDC power. RUN (green) indicates LI is operational and CPU is ac-ON cessing image table information. OFF -Indicates LI is in self-diagnostics or has FLASHING - Indicates LI is running but one or more drops on its channels have been programmed to halt. (Bits 1-8 of the L1 channel control register.) HALT (red) ON -Indicates L1 is in self-diagnostics and/or has halted operation. Indicates LI is fully operational and CPU is OFF accessing image table information. FLASHING - Indicates LI is running but one or more drops on its channels have been programmed to halt. (Bits 1-8 of the LI channel control register.) CHANNEL ERROR (red) ON -Indicates LI cannot communicate with one or more of its drops which are shutdown. OFF -Indicates all drops operational. FLASHING - Indicates a module failure on a drop has caused a drop to shutdown on this channel. MODULE ERROR (red) ON -Indicates a self diagnostic error or internal timeout error has been recognized and halted the CPU. OFF -Indicates LI is operational even though a channel HALT or CHANNEL ERROR LED may be ON. FLASHING - Not valid

Figure 5.1 - LI LED Explanation

# REMOTE INTERFACE

All lights OFF indicates loss of 5VDC power.

#### RUN (green)

ON - Indicates remote drop is operational.

OFF - Indicates RI is shutdown or has not been initialized. Outputs will de-energize provided the shutdown is not a direct result of a communication error, and the Freeze function is also selected. (Some register modules are capable of maintaining register information.)

FLASHING - Indicates CPU is in Disable Outputs mode. (50% ON, 50% OFF alternately with HALT LED.)

BLINKING - Indicates LI HALT bit for the drop is set. (5% ON, 95% OFF, alternately with HALT LED.)

#### HALT (red)

ON - Indicates RI is shutdown. If the only LED ON, it indicates rack was shutdown due to program control or has not been initialized

OFF - Indicates remote drop is operational.

FLASHING - Indicates CPU is in Disable Outputs mode. (50% ON, 50% OFF alternately with RUN LED.)

BLINKING - Indicates LI HALT bit for the drop is set. (95% ON, 5% OFF, alternately with RUN LED.)

# CHANNEL ERROR (red)

ON - Indicates invalid or loss of communications between RI and LI. HALT LED will also be ON.

OFF - Indicates valid communication between RI and I I

# I/O ERROR (red)

ON - Indicates: (HALT LED should also be ON.)

A read after write error to an output.

Error caused by a malfunctioning register module.

RI malfunction.

OFF - Indicates RI is properly communicating with modules in same rack.

FLASHING - Indicates outputs and inputs are frozen (ON or OFF).

# MODULE ERROR (red)

ON - Indicates self diagnostic error or internal timeout error has occurred.

OFF - Indicates RI is operational although drop may be shutdown due to system shutdown or program control.

FLASHING - Not valid

# 3. Control Registers

Determine the contents of the respective Channel Control Registers

- A. Channel 1, L1 register (\$8162 for the first L1 in the system)

- B. Channel 2, LI register (S8161 for the first LI in the system) refer to Appendix D, LI Control/Status Registers for further information.

Progressive evaluation and interpretation of these bits indicate how to resolve, eliminate or compensate for the system malfunction.

# 5.5 Undervoltage Lockout Circuit (ULC) Operation

Series O and later Local Interface devices are designed with an on-board DC Undervoltage Lockout Circuit that monitors the incoming DC voltage level at the edge connector of the slot in which the LI Module resides. If the incoming DC voltage falls below 4.6 volts, the CRM-210, 211 enters a HALT state and no longer communicates with the processor on the rack, or its associated I/O. All LEDs on the front of the module are turned off and the processors in the CPU rack are halted.

When incoming DC voltage rises above 4.6V, the CRM-210/211 executes a standard power-up initialization sequence. When recovering from a ULC error, a 902 error code is posted in the L1 error register (e.g. 8163).

Even though Series O and later Local Interface devices enter a HALT state when the incoming DC voltage falls below 4.6VDC, other devices in the same rack may remain poweredup, since the ULC resides in only selected SY/MAX Modules. Some possible causes for the ULC being engaged are, an overloaded power supply or a poor cable connection between the power supply and the rack. If these or other problems arise, correct the respective problem first, then normal operation can be resumed.

# 5.6 Module Replacement Procedure

If it is necessary to replace components, use the following procedure:

- 1. Keyswitch the CPU to HALT prior to removing power.

- Remove power from all rack assemblies in a system.

- 3. Disconnect communication cabling and remove module.

- Set switches on replacement module.

- 5. Install module and attach communication cabling.

- 6. Reapply power to system.

- 7. Restart the system and verify operation.

NOTE: ERROR 901 identifying register corruption may require toggling processor keyswitch several times to clear the error.

# 5.7 LI/RI Communication Restart (Push Button)

Whenever communication is lost between the Ll and an RI, an error code is generated and the Channel Error LED will be ON. Communication may be lost because of the following:

- 1. Loss of power at the Local CPU Rack.

- 2. A broken cable between the LI and RI.

- 3. Loss of power at a Remote Rack (DROP).

- 4. Hardware malfunction.

Reestablishment of LI/RI communications will always be attempted each time any of the following occurs:

# LI/RI LED RESPONSES TO ERRORS

|               |      |                        |                  | uu              | EMTS.                  |                  |                 |             |                  |              | At LIGH         | (16         |                  |             |                 | u                             |                 | OPERATING                        |

|---------------|------|------------------------|------------------|-----------------|------------------------|------------------|-----------------|-------------|------------------|--------------|-----------------|-------------|------------------|-------------|-----------------|-------------------------------|-----------------|----------------------------------|

| CPU<br>STATUS |      | WITH                   | A DROP FA        | ILED            | WITH ALL I             | DROPS OPE        | RATIONAL        |             | FAILE            | D 080P       |                 |             | OPERATIO         | N DROP      |                 | CHAMBE                        | BITS            | CONDITION                        |

| NUM/          | MALT | CHANNEL<br>RUN<br>HALT | CHANNEL<br>ERROR | MODULE<br>ERROR | CHANNEL<br>RUN<br>HALT | CHANNEL<br>ERROR | MODULE<br>ERROR | RUN<br>HALT | CHANNEL<br>ERROR | I/O<br>ERROR | MODULE<br>ERROR | RUN<br>HALT | CKANNEL<br>ERROR | IO<br>ERROR | MODULE<br>ERROR | FAILURE<br>OVERRIBE<br>BIT 13 | FREEZE<br>BIT 9 |                                  |

| k             | С    | _                      | -                | ۲.              | k                      | 0                | 0               | R           | 0                | tı           | 0               | ¥           | U                | 0           | 0               |                               |                 | Seeml (CPC Run)                  |

| r             | С    | _                      | j -              | €:              | R                      | 0                | 0               | F           | 0                | tı           | O               | F-          | 4)               | t)          | 11              |                               | -               | Drables Outputs (19              |

| R             | С    | -                      | -                | C               | <br>                   | 0                | 0               | 8           | 0                | ti           | O               | н           | ()               | u           | 0               |                               |                 | Cownil Register<br>Hati Bi: Sei  |

| O             | ١.   | R                      | 1                | ı               | K                      | υ                | υ               | н           | U                | -0           | Λ               | н           | 13               | 0           | ti              | 1)                            | £1              | Transmission Effor               |

| 0             | F    | R                      | F                | ١.              | R                      | i o              | 0               | Н           | 0                | 1            | 1)              | н           | 0                | "           | 0               | D                             | t1              | Bus of Real After<br>Write firm  |

| 0             | F    | R                      | 1                |                 | R                      | 0                | O               | н           | 0                | ŀ            | X               | н           | 0                | ŀ           | 0               | - 13                          | ١.              | Transpission End                 |

| α             | F    | Ř                      | F                | ı               | R                      | 0                | 0               | н           | o                | 1            | 0               | R           | n                | ŀ           | 0               | 0                             | ı               | Bus of Read After<br>Write Error |

| R             | G    | ĸ                      | ı                | Ç               | k                      | . 0              | 0               | Н           | 0                | 0            | X               | R           | 0                | D           | 0               | 1                             | 0               | Transmission Liner               |

| R             | r:   | R                      | F                | с               | k                      | 0                | 0               | н           | o                | '            | ()              | R           | o                | "           | o               | '                             | 0               | Rus or Read After<br>Write Effor |

| Ŗ             | С    | R                      | 1                | С.              | R                      | 0                | 0               | п           | 0                | F            | X               | R           | o                | u .         | 0               | ŧ                             | 1               | Transmission I mor               |

| R             | ۲.   | R                      | +                | 6:              | k                      | 0                | 0               | R           | 0                | ı            | o               | R           | 0                | u           | ţ1              | 1                             | I               | Bus of Read After<br>Work Lines  |

- 0 = OFF

- I = ON

- = NOT APPLICABLE

- R = RUNH = HALT

- F = FLASHING (50% Duty Cycle)

- B = BLINKING (Halt 95% ON, Run 5% ON)

- X = EITHER ON or OFF (2)

- NOTES: 1. Run light on LI signifies that LI is operational no matter what error conditions(s) exist within the RI or CPU.

- The state of the remote channel error light is dependent on which device detected communication error first: On-remote and OFF-local.

## LI/RI FAULT STATUS

|                    |        |                        |         | DROP       | DROP FAULT |              |               |                   | CHANNEL FAULT<br>(Transmission Loss) |                  |               |               |        | PROGRAM HALTED DROP<br>See Notes |               |                   |         |                  |         |         |        |              |

|--------------------|--------|------------------------|---------|------------|------------|--------------|---------------|-------------------|--------------------------------------|------------------|---------------|---------------|--------|----------------------------------|---------------|-------------------|---------|------------------|---------|---------|--------|--------------|

|                    |        |                        |         | FAILED     | DROP       |              | OP            | ERATIO            | NAL DE                               | OP .             |               | FAILED        | DROP   | )                                | OF            | ERATIO            | NAL DR  | OP .             | HALTE   | D OPER  | ATION  | DROP         |

| FAILURE<br>OVERIDE | FREEZE | CPU<br>STATUS<br>AFTER |         | CAL<br>AGE |            | OTE<br>TOP   |               | CAL<br>NGE        |                                      | MOTE<br>ROP      |               | CAL<br>AGE    |        | MOTE<br>ROP                      |               | CAL<br>AGE        |         | IOTE<br>IOP      | LO      | CAL     |        | MOTE<br>ROP  |

| BIT 13             | BIT 9  | FAULT                  | INPLITS | OUTPUTS    | INPUTS     | outruts      | INPUTS        | OUTPUTS           | INPUTS                               | OUTPUTS          | UNPUTS        | OUTPUTS       | INPUTS | KX TPLITS                        | INPUTS        | OUTPUTS           | INPLITS | OUTPUTS          | INPUTS  | OCTPUTS | INPUTS | OUTPUTS      |

| 0                  | 0      | HALT                   | CLEAR   | CLEAR      | -          | TURN<br>OFF  | CLEAR         | CLEAR             |                                      | TURS<br>OFF      | CLEAR         | CLEAR         |        | TURN<br>OFF                      | CLEAR         | CLEAR             | _       | TURN<br>OFF      | UPDATE  | CLEAR   |        | TI RN<br>OFF |

| 0                  | ı      | HALT                   | CLEAR   | CLEAR      |            | TL RN<br>OFF | LAST<br>STATE | LAST<br>STATE     |                                      | LAST<br>STATE    | LAST<br>STATE | LAST<br>STATE |        | LAST<br>STATE                    | LAST<br>STATE | LAST<br>STATE     | -       | LASI<br>SIATE    | L POATE | CLŁAR   | -      | TURN<br>(MF) |

| 1                  | ı)     | RUN                    | CLEAR   | CLEAR      |            | TURN<br>OFF  |               | L PDAJE<br>LADDAR |                                      | UPDATE<br>LADDER | CLEAR         | CLŁAR         | _      | TURN<br>OHF                      | LPDATE        | 1 PDATE<br>LADDER |         | LPDATE<br>LADOER | LPBATE  | CLEAR   | _      | TURN<br>OHE  |

|                    | -      | RUN                    | CLEAR   | CLEAR      | _          | TURN<br>OFF  |               | LPDATE<br>LADDER  |                                      | UPDATE<br>LADDER | LAST<br>STATE | LAST<br>STATE | _      | LAST<br>STATE                    | UPDATE.       | LPDATE<br>LADDER  |         | UPDATE<br>LADDER | имин    | CLEAR   | _      | FURN<br>OH   |

## NOTES:

- 1. LI HALT Bit refers to bits 1 to 8 of the LI channel control data register.

- 2. Regardless of how outputs on a drop get frozen, if communication is re-established, the drop will reset, clear all outputs and local image table information for that drop, and stay in the halted mode until restarted.

- 3. Restarting the system may be done in any of the following ways.

- A. Toggling the CPU keyswitch

- B. Power cycling the local (CPU) rack.

- C. Auto Restart function of the LI/RI system.

- D. Pushing the Ll Restart button.

For more detailed information, refer to Section 5.6, LI/RI Communications Restart (Push Button).

4. If the CPU halts its execution due to an error, turning the keyswitch to HALT will not reset frozen outputs on any of the remote drops even if valid LI/RI communication is present.

Figure 5.4 - CPU and LI/RI Response to I/O Faults

- Toggling the CPU keyswitch out of HALT.

- Power cycling the power to the local CPU racks while the CPU is in RUN or DISABLE OUTPUTS.

- Power cycling the remote drops while the Failure Override Bit is ON.

- Pushing the LI restart push button while the Failure Override Bit is ON and the CPU is in RUN or DISABLE OUTPUTS.

The RESTART button is operational when all the following exists:

- 1. CPU must be running.

- Communications error must have originated on one of the LI channels.

- 3. Failure Override Bit must be ON.

- Valid communications must be able to be established to the affected racks, or else no change of state will occur.

NOTE: The RESTART button will only restart drops which are shutdown due to communications errors. It will have no effect if a local (CPU) rack error exists.

WARNING: Pressing the RESTART (RESET) button on the front of the LI module may cause outputs to turn ON or OFF.

#### 5.7.1. FROZEN DROP RESET

An operational drop with frozen outputs may be reset by:

- 1. Power cycling the remote drop.

- Setting the drop HALT bit ON while the Failure Override Bit is ON and CPU are operational. For more information on how to apply these bits, refer to Appendix D, LI Control/Status Registers.

- Turning keyswitch to HALT providing the CPU rack is operational, no errors exist.

# 5.8 CPU and LI/RI Response to Faults

Figure 5.4 depicts how a system will respond to a detected fault condition within the LI/RI portion of the system.

# **5.9 Obtaining Additional Assistance**

If additional assistance is needed, the following must be available.

- 1. A concise statement of the problem. Also, determine what the system is actually doing.

- 2. A physical description of the system indicating the quantities and types of the following:

- A. Inputs and outputs.

- B. Channels.

- C. Drops.

- D. Registers per drop.

- E. I/O per drop.

- 3. Is this a start-up of a new system or an addition or repair to a previously operable system?

- 4. How long has the system been operational?

- 5. Have any overriding control register bits been set?

- 6. What is the rack addressing as seen on the CRT screen?

- 7. Check contents of the following registers:

- A. CPU ERROR CODE

- B. LI ERROR CODE

- C. LI CHANNEL CONTROL/STATUS

- 8. Describe the equipment involved:

|                         | Qty. | Serial Number | Class | Type | Series | Revision |   |

|-------------------------|------|---------------|-------|------|--------|----------|---|

| Processor               |      |               |       |      |        |          | 1 |

| Local Interface(s)      |      |               |       |      |        |          |   |

| Remote Interface(s)     |      |               |       |      |        |          |   |

| Bus Expander(s)         |      |               |       |      |        |          |   |

| Rack Assembly(s)        |      |               |       |      |        | 1        |   |

| Register Module(s)      |      |               |       |      |        | 1        |   |

| Communication Module(s) |      |               |       |      |        |          |   |

| CRT Programmer          |      |               |       |      |        |          |   |

| Loader/Recorder         |      |               |       |      |        |          |   |

| Other Equipment         |      |               |       |      |        |          |   |

Figure 5.5 - Equipment List

# APPENDIX A

# A.O LI/RI UPDATE TIME

# A.1 General Information

This appendix provides equations for calculation of the LI/RI update time.

Update time refers to the time required to pass information in either direction between the LI image table and the RI image table.

Update time should not be confused with throughput time. Throughput time is the time required from the actuation of an input until an output action occurs. Throughput time also includes I/O module response time as well as CPU processing time. Further information regarding throughput (overall system response) is covered in the Planning and Installation Guide Instruction Bulletin, 30598-175.

# A.2 Channel Update Time

Channel update time is dependent on the update time of the drop with the greatest number of registers assigned to it and the total number of registers on the channel. Therefore, by calculating the update time of that particular drop, the worst case channel update time may be determined.

# **A.3 Drop Update Time**

One of two equations are used to calculate drop update time. For the purpose of these equations, drops will be put into two categories, digital and register. The digital drop is a pure digital drop (8 or less registers\*) with no register modules. While the register drop will contain register modules or a combination of register and digital modules.

\* For 9 or more registers, use register drop equations.

# A.4 Update Time Equation Variables

D - Total digital drops on the channel. (0-8)

R = Total register drops (or digital/register drops) on the channel. (1-8)

DR = Total register addresses assigned to all digital drops. (0-64)

RR = Total register addresses assigned to all register drops. (1-255)

X = Register addresses assigned to the drop being evaluated. (1-8) If more than 8 registers are assigned, use X = 8.

Note that actual performance times may be better than calculations for channels with many registers.

# A.5 Drop Update Time Equations

Use this equation for a channel with only digital drops.

Digital Channel Drop Update Time (ms) = 2.31D + DR + X + 0.79

Use this equation for all other remote I/O channels.

Register Channel Drop Update Time (ms) = 2.31D + DR + 3.15R + 1.24(RR + X) + 1.52

# A.6 Example #1

This example works out the drop update time for a purely digital channel. This example has the following relevant attributes.

Figure A.1 - Digital Channel

CHANNEL 1 Consists of one drop and 4 registers.

DROP #1 Consists of 4 registers used for digital I/O.

CHANNEL 2 Not used.

Channel 1 Digital Drop Update Time = 2.31D + DR + X + 0.79 = 2.31(1) + (4) + (4) + 0.79 = 11 lms

# A.7 Example #2

This example works out the drop update time equation for a combinational (register) channel.

Figure A.2 - Register Channel

CHANNEL I Consists of two drops and 32 registers.

DROP #1 Consists of 8 registers used for digital I/O. DROP #2 Consists of 24 registers, some used for data storage.

CHANNEL 2 Consists of one drop and 56 registers

DROP #1 Consists of 56 registers used for data storage.

Note that only the register drop update time equations can be used since neither channel has only digital drops.

# Channel 1 Drop Update Time

$$=2.31D$$

+ DR + 3.15R + 1.24(RR + X) + 1.52

= 2.31(1) + (8) + 3.15(1) + 1.24(24 + 8) + 1.52

= 54.7ms.

# Channel 2 Drop Update Time

$$= 2.31D$$

+ DR + 3.15R + 1.24(RR + X) + 1.52

= 2.31(0) + (0) + 3.15(1) + 1.24(56 + 8) + 1.52

= 84.0ms.

# **A.8 Register Optimization**

By allocating only the number of registers which will be used by a register module, channel update time can be minimized. For example, if only five of the 16 registers of a RIM 141 BCD Output Module are actually needed, assign only five. This register reduction of 16 to 5 will result in a 15ms channel update time savings.

# APPENDIX B --- ERROR CODES

# **B.1 Introduction And Description**

#### **B.1.1 GENERAL INFORMATION**

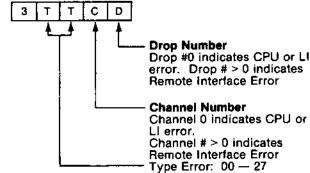

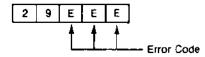

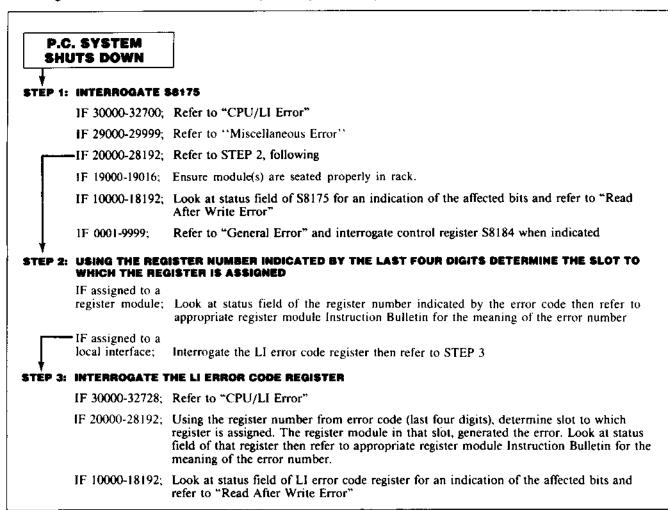

Errors detected by the processor and error codes annunciated on the CRT provide the operator with information useful in isolating problems.

Some errors are indicated as messages on the screen display while other error indications involve error code numbers. Since the messages are self explanatory, this appendix deals directly with the numbered error codes.

These error code numbers can be broken into two general categories and are indicated in different locations on the CRT screen.

In the first category are the **peripheral to PC system** interaction errors of which 3 classifications of error codes exist. These errors are indicated at the bottom of the screen display or for some special cases, in the status register of a communications rung.

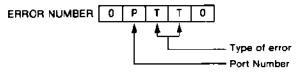

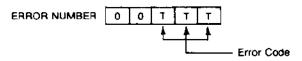

In the second category are the PC system operational errors which are errors detected within the processor or any one of the modules contained in a programmable controller system. These errors are indicated in the STATUS Mode display next to the label ERROR NUMBER. The number displayed is also the number contained in the error code control register 8175 or possibly in a Local Interface Module error code control register (when using remote 1/O).

# B.1.2 PERIPHERAL TO PC SYSTEM INTERACTION ERRORS

These types of errors are associated with attempts to perform illegal operations with the processor or the communication hardware is not functioning properly. This category of error will only be generated when using the keyboard to command processor operations or when the processor is attempting communication with other responding devices.

The three classifications of peripheral to PC system interaction error codes are: Processor, Transmission, and Tape. When an error occurs while a programmer is connected to the processor, one of these messages will be shown on the display along with a number. Should an error occur during the execution of a processor communication rung a Processor Error will be used to indicate the fault. The number code will be shown when the status register of the communication rung is displayed.

## **Processor Errors**

These errors indicate that the operation attempted was not successfully completed. The error code numbers range from 01 thru 99. To resolve the error situation, check the error code description in the following table, use the CLEAR key to clear the error indication if the error has been displayed on a programmer, and take the appropriate recourse action. Error codes indicated by an asterisk (\*) in the following Error Code Table, may also be displayed in the status register of a communications rung.

# PROCESSOR ERROR CODE TABLE

| PROCESSOR ERROR CODE TABLE |                                                                                                                                                                                                     |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Error<br>Code<br>No        | Error Description                                                                                                                                                                                   |  |  |  |  |

| 01*                        | Illegal protocol opcode, the device does not recognize the instruction. Reenter the desired operation.                                                                                              |  |  |  |  |

| 02                         | Illegal intermediate code format. Reenter the desired operation.                                                                                                                                    |  |  |  |  |

| 03*                        | An illegal address has been attempted.                                                                                                                                                              |  |  |  |  |

| 04                         | Illegal rack addressing has been attempted.                                                                                                                                                         |  |  |  |  |